# **Application Manual**

# Real Time Clock Module RA4000CE/RA8000CE

| Product name   | Product number  |

|----------------|-----------------|

| RA4000CE YB A0 | X1B000491A00115 |

| RA4000CE YB B8 | X1B000491A00915 |

| RA4000CE YB C0 | X1B000491A01015 |

| RA4000CE YB D0 | X1B000491A01115 |

| RA4000CE YB E8 | X1B000491A01915 |

| RA8000CE YB A0 | X1B000501A00115 |

| RA8000CE YB B8 | X1B000501A00915 |

| RA8000CE YB C0 | X1B000501A01015 |

| RA8000CE YB D0 | X1B000501A01115 |

#### NOTICE: PLEASE READ CAREFULLY BELOW BEFORE THE USE OF THIS DOCUMENT

- The content of this document is subject to change without notice. Before purchasing or using Epson products, please contact with sales representative of Seiko Epson Corporation ("Epson") for the latest information and be always sure to check the latest information published on Epson's official web sites and resources.

- 2. This document may not be copied, reproduced, or used for any other purposes, in whole or in part, without Epson's prior consent.

- 3. Information provided in this document including, but not limited to application circuits, programs and usage, is for reference purpose only. Epson makes no guarantees against any infringements or damages to any third parties' intellectual property rights or any other rights resulting from the information. This document does not grant you any licenses, any intellectual property rights or any other rights with respect to Epson products owned by Epson or any third parties.

- 4. Using Epson products, you shall be responsible for safe design in your products; that is, your hardware, software, and/or systems shall be designed enough to prevent any critical harm or damages to life, health or property, even if any malfunction or failure might be caused by Epson products. In designing your products with Epson products, please be sure to check and comply with the latest information regarding Epson products (including, but not limited to this document, specifications, data sheets, manuals, and Epson's web site). Using technical contents such as product data, graphic and chart, and technical information, including programs, algorithms and application circuit examples under this document, you shall evaluate your products thoroughly both in stand-alone basis and within your overall systems. You shall be solely responsible for deciding whether to adopt/use Epson products with your products.

- 5. Epson has prepared this document carefully to be accurate and dependable, but Epson does not guarantee that the information is always accurate and complete. Epson assumes no responsibility for any damages you incurred due to any misinformation in this document.

- 6. No dismantling, analysis, reverse engineering, modification, alteration, adaptation, reproduction, etc., of Epson products is allowed.

- 7. Epson products have been designed, developed and manufactured to be used in general electronic applications and specifically designated applications ("Anticipated Purpose"). Epson products are NOT intended for any use beyond the Anticipated Purpose that requires particular quality or extremely high reliability in order to refrain from causing any malfunction or failure leading to critical harm to life and health, serious property damage, or severe impact on society, including, but not limited to listed below ("Specific Purpose"). Therefore, you are strongly advised to use Epson products only for the Anticipated Purpose. Should you desire to purchase and use Epson products for Specific Purpose, Epson makes no warranty and disclaims with respect to Epson products, whether express or implied, including without limitation any implied warranty of merchantability or fitness for any Specific Purpose. Please be sure to contact our sales representative in advance, if you desire Epson products for Specific Purpose: Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and their control equipment / Medical equipment / Relay equipment to be placed on sea floor / Power station control equipment / Disaster or crime prevention equipment / Traffic control equipment / Financial equipment Other applications requiring similar levels of reliability as the above

- 8. Epson products listed in this document and our associated technologies shall not be used in any equipment or systems that laws and regulations in Japan or any other countries prohibit to manufacture, use or sell. Furthermore, Epson products and our associated technologies shall not be used for the purposes of military weapons development (e.g. mass destruction weapons), military use, or any other military applications. If exporting Epson products or our associated technologies, please be sure to comply with the Foreign Exchange and Foreign Trade Control Act in Japan, Export Administration Regulations in the U.S.A (EAR) and other export-related laws and regulations in Japan and any other countries and to follow their required procedures.

- 9. Epson assumes no responsibility for any damages (whether direct or indirect) caused by or in relation with your non-compliance with the terms and conditions in this document or for any damages (whether direct or indirect) incurred by any third party that you give, transfer or assign Epson products.

- 10. For more details or other concerns about this document, please contact our sales representative.

- 11. Company names and product names listed in this document are trademarks or registered trademarks of their respective companies.

# **ETM64E Revision History**

| Rev. No. | Date       | Page                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|----------|------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 01       | 6.Dec.2021 | All                                                                                                    | New established                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|          |            | 8                                                                                                      | 2.2.1 Power-On Sequence.  Old: Before turning the power supply back on after being turned off, be sure to maintain an OFF period with the V <sub>DD</sub> pin set to the GND level for at least 10 seconds after turning off.  New: Before turning the power supply back on after being turned off, be sure to maintain an OFF period with the V <sub>DD</sub> pin set to the GND level for at least 100 ms after turning off. |  |  |  |  |  |  |  |

|          |            | Replacement : <i>Figure 3.11 Clock/Calendar Counter Configure</i> Address was corrected of Figure 3.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|          |            | 25, 26, 27                                                                                             | Register name corrected: Page_25  Origin: SEC_BIN0_MIR to SEC_BIN4_MIR.  Correct: SEC_BIN0 to SEC_BIN4.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|          |            | 27                                                                                                     | ·Origin: Registers SEC_BIN0 to SEC_BIN4 (Addresses 0x00 to 0x04) ·Correct: Registers SEC_BIN0 to SEC_BIN4 (Addresses 0x12 to 0x16)                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 02       | 5.Aug.2022 | 65, 66                                                                                                 | -Changed "BIN mode" of "0x00 ~ 0x04" of register list Bank0 from "SEC_BIN0 ~ 4" to "Not used"Changed "BIN mode" of "0x12 ~ 0x16" of register list Bank1 from "SEC_BIN0_MIR ~ 4_MIR" to "SEC_BIN0 ~ 4". Symbol meanings                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|          |            | 72, 80                                                                                                 | -Deleted "BIN mode", "SEC_BIN0-4" of "0x00 ~ 0x04" of Bank0 in the detailed register explanation.  -Changed the register names of "BIN mode", "SEC_BIN0_MIR-4_MIR" of "0x12 ~ 0x16" of Bank1 in the detailed register description to "SEC_BIN0-4", Rename. Moved the function description from "SEC_BIN" of "0x00 ~ 0x04". Move.                                                                                               |  |  |  |  |  |  |  |

|          |            |                                                                                                        | Power-On Characteristics                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|          |            |                                                                                                        | ·old: To ensure that power-on reset takes effect, maintain the VDD =                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|          |            | 100                                                                                                    | GND condition for at least <b>10 seconds</b> after power-off.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|          |            |                                                                                                        | ·new: To ensure that power-on reset takes effect, maintain the VDD is                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|          |            |                                                                                                        | GND level condition for at least <b>100ms</b> after power-off.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

#### **Preface**

This document is the application manual for describing the functions, control method, specifications, and electrical characteristics of Seiko Epson Real-Time Clock (RTC) modules RA4000CE and RA8000CE. This manual is provided for designers who develop products using the RA4000CE/RA8000CE.

The RA4000CE is accessed through SPI from the host; the RA8000CE is accessed through I<sup>2</sup>C-Bus. For the operations and control methods of these interfaces, refer to a host device manual or other documents.

## Notational conventions and symbols in this manual

#### **Notation of Numbers**

This manual describes numbers in decimal, binary, and hexadecimal notations.

Decimal Examples: 1, 10, 123 (general values, date and time, etc.)

Binary Examples: 0b0, 0b10, 0b1111 (control bit setting values, read values, etc.)

Hexadecimal Examples: 0x0, 0xF, 0xFF (addresses, register setting values, etc.)

#### **Notation of Register and Bit Names**

This manual describes register and bit names as shown below.

Register name: Register SEC

Bit name: TSTP INTE.STOP bit

This represents the STOP bit in Register TSTP INTE.

TCTL.FSEL[1:0] bits

This represents two bits in Register TCTL: FSEL1 and FSEL0 bits.

#### **Notation of Channel Numbers**

The time stamp function has provided a pin and control bit for each channel that has the same function as the other channels. The pin and bit names contain a channel number (e.g., 1 and 2). This manual uses "n" for the channel numbers to explain the pins and bits for all channels collectively, if there is no need to be individually described. Furthermore, "\*\*\*" is used as a different part of a bit name for describing plural bit names that have a same part.

Pin name: EVIN1 and EVIN2  $\rightarrow$  EVINn

Bit name: EVINn EN.EVIN1EN and EVINn EN.EVIN2EN

→ EVINn EN.EVINnEN

EVIN*n* EN.EVIN1CPEN, CAP EN.VTMPLCPEN, and others

→ \*\*\*CPEN

# **Table of Contents**

| ETM6    | 4E Revision History                                                     | i   |

|---------|-------------------------------------------------------------------------|-----|

|         | ce                                                                      |     |

|         | onal conventions and symbols in this manual                             |     |

|         | Notation of Numbers                                                     |     |

|         | Notation of Register and Bit Names                                      | ii  |

|         | Notation of Channel Numbers                                             |     |

| Table   | of Contents                                                             | iii |

| 1 Overv | /iew                                                                    | 1   |

|         |                                                                         |     |

| 1.1 BI  | ock Diagram                                                             |     |

|         | RA4000CE (3-wire SPI)                                                   |     |

|         | RA4000CE (4-wire SPI)                                                   |     |

|         | RA8000CE (I <sup>2</sup> C-Bus)                                         |     |

| 1.2 Pi  | n                                                                       |     |

| 1.2.1   | Pin Alignment Diagram                                                   |     |

|         | RA4000CE                                                                |     |

|         | RA8000CE                                                                |     |

| 1.2.2   | Pin Descriptions                                                        |     |

|         | Symbol Meanings                                                         | 6   |

| 2 Powe  | r Supply and Initialization                                             |     |

|         |                                                                         |     |

| 2.1 Pc  | ower Supply                                                             | 8   |

| 2.2 Ini | tialization                                                             | 8   |

| 2.2.1   | Power-On Sequence                                                       |     |

| 2.2.2   | Oscillation Start-UP Time                                               |     |

| 2.2.3   | Initial Settings                                                        | 11  |

|         | Initial Setting Procedure (for models without the /RST output function) | 11  |

|         | Initial Setting Procedure (for models with the /RST output function)    |     |

| 2.3 Or  | perating Mode                                                           | 13  |

|         | POR enabled                                                             |     |

|         | Initial mode                                                            |     |

|         | Normal mode                                                             |     |

|         | Safe mode                                                               |     |

| 2 Euros | tions                                                                   | AE  |

|         |                                                                         |     |

|         | ost Interface                                                           |     |

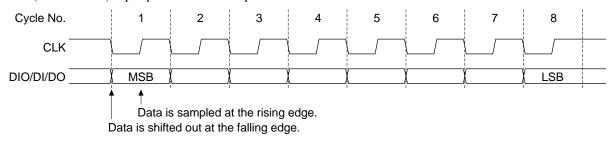

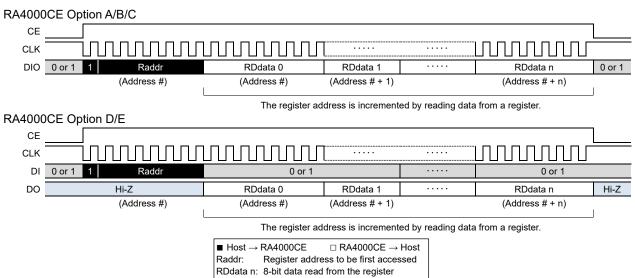

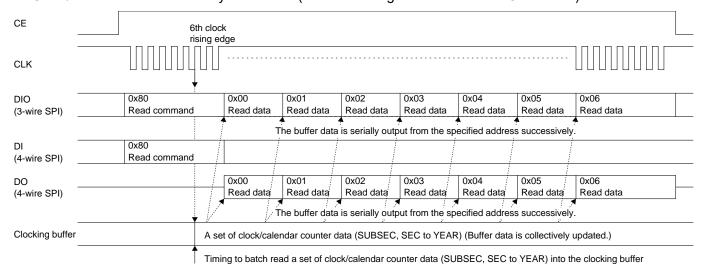

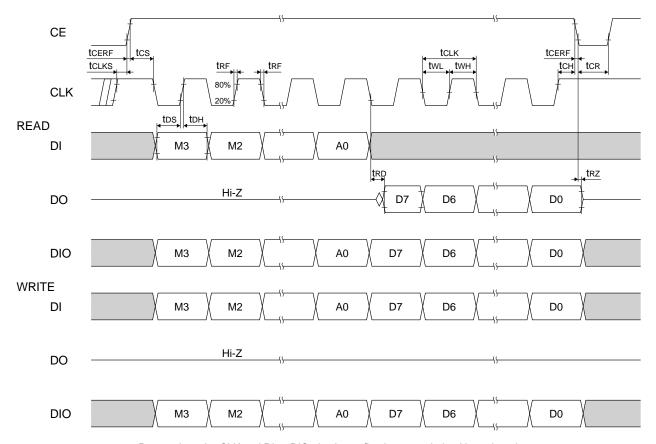

| 3.1.1   | Accessing to RA4000CE Registers (SPI)                                   |     |

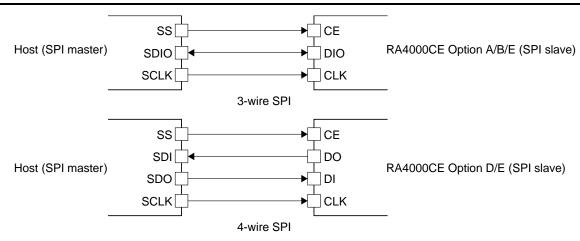

|         | SPI Interface Pins                                                      |     |

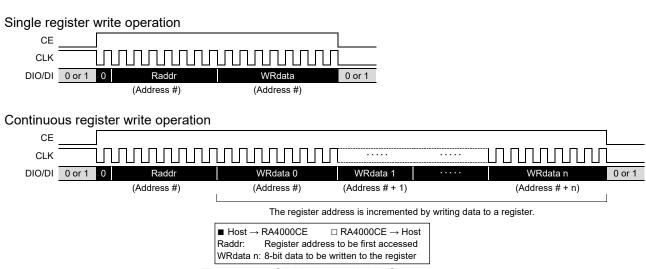

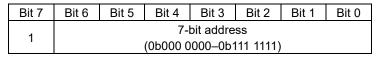

|         | Writing Data to Registers                                               |     |

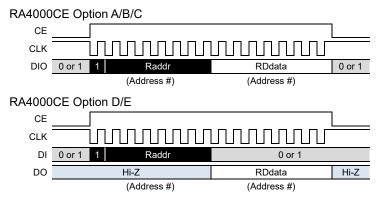

| 0.4.5   | Reading Data from Registers                                             |     |

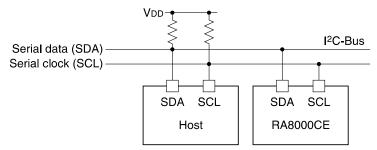

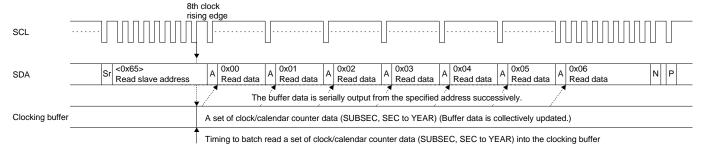

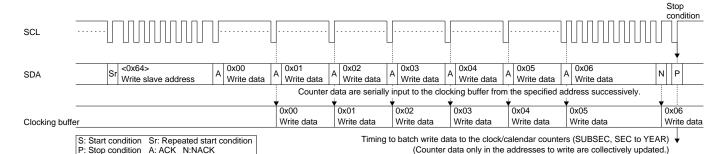

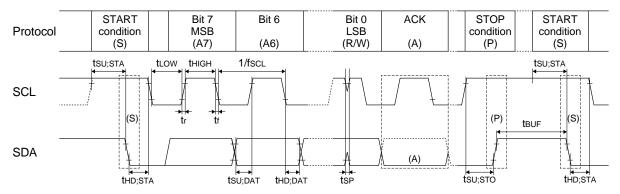

| 3.1.2   | Accessing to RA8000CE Registers (I <sup>2</sup> C-Bus)                  |     |

|         | I <sup>2</sup> C-Bus Interface Pins                                     |     |

|         | Slave Address                                                           |     |

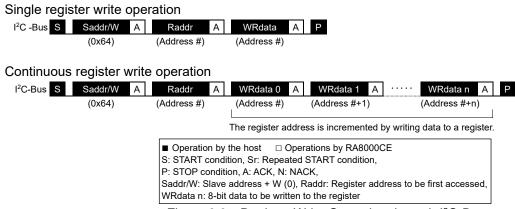

|         | Writing Data to Registers                                               |     |

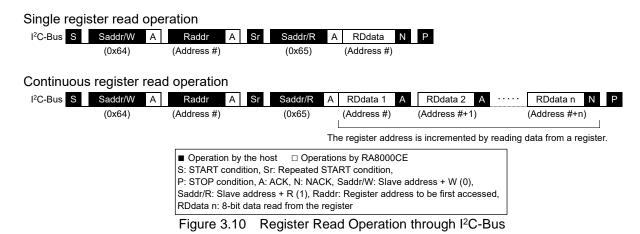

|         | Reading Data from Registers                                             |     |

| _       | ock and Calendar Function                                               | -   |

| 3.2.1   | Overview                                                                |     |

| 3.2.2   | Operations                                                              |     |

|         | BCD Mode and BIN Mode                                                   |     |

|         | Accessing Clock/Calendar Counter through Clocking Buffer                |     |

|         | Initial Setting and Starting Clock/Calendar                             |     |

|         | Reading Clock/Calendar Data                                             |     |

|         | Reading/Writing 1/1024-Second Data                                      |     |

|         | Clock/Calendar Counter Stop Procedure                                   |     |

|         | Leap Year Determination                                                 |     |

|         | Leap Second Correction Procedure                                        |     |

|         | =                                                                       |     |

ETM64E-02

|          | nperature Compensation Function                                          |                 |

|----------|--------------------------------------------------------------------------|-----------------|

| 3.3.1    | Operations Setting Temperature Compensation Interval                     |                 |

|          | Temperature Compensation Operation Flag: VTMPLF flag (0x0E)              |                 |

| 2.4 Th.  |                                                                          |                 |

| 3.4.1    | eoretical Regulation Function Operations                                 |                 |

| 3.4.1    | Theoretical Regulation Operation                                         |                 |

|          | Setting Correction Amount                                                |                 |

|          | Enabling Theoretical Regulation                                          |                 |

|          | Disabling Theoretical Regulation                                         | 32              |

| 3.4.2    | Influence of Theoretical Regulation to Other Functions                   | 32              |

| 3.5 Tin  | ne Update Interrupt Function                                             | 33              |

| 3.5.1    | Overview                                                                 |                 |

| 3.5.2    | Operations                                                               |                 |

|          | Selecting Interrupt Period                                               |                 |

|          | Interrupt Enabling/Disabling Procedure                                   |                 |

|          | Interrupt Operations                                                     |                 |

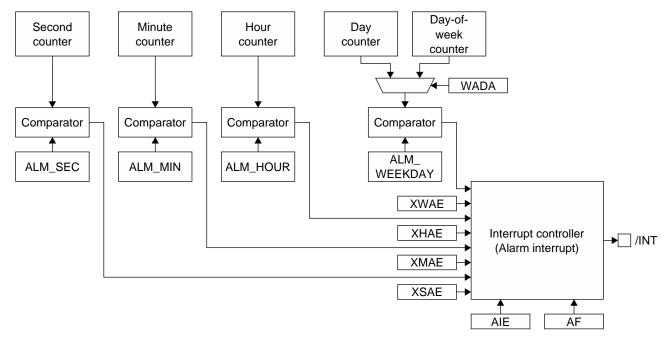

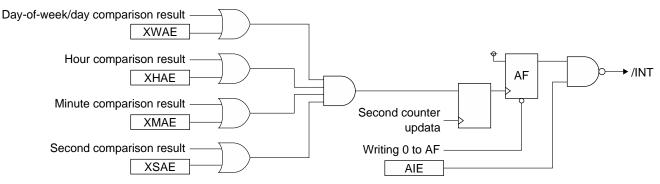

|          | rm Function                                                              |                 |

| 3.6.1    | Overview                                                                 |                 |

| 3.6.2    | Operations                                                               |                 |

|          | Alarm Setting ProcedureAlarm Setting Examples                            |                 |

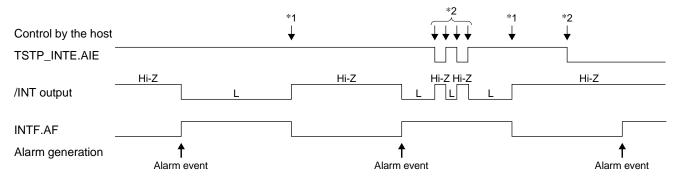

|          | Alarm Interrupt                                                          |                 |

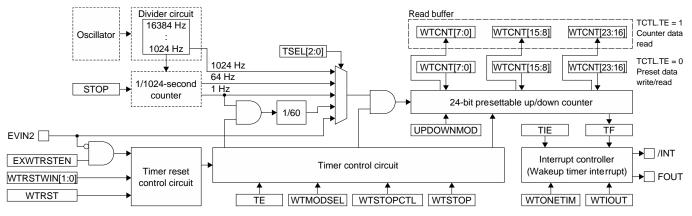

| 27 Wa    | keup Timer Function                                                      |                 |

| 3.7.1    | Overview                                                                 |                 |

| 3.7.2    | Operations                                                               |                 |

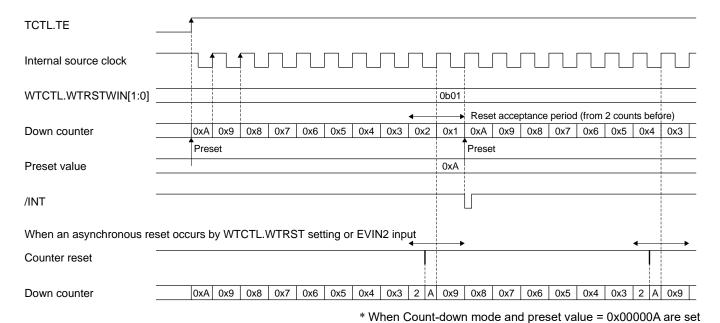

|          | Source Clock                                                             |                 |

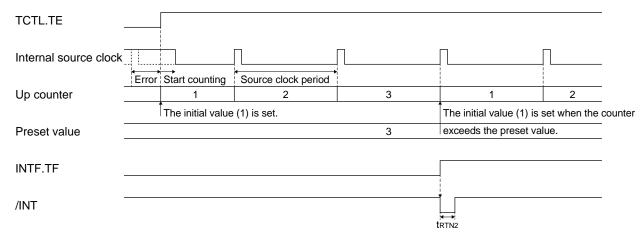

|          | Count-Up/Down Mode                                                       |                 |

|          | Preset Data (wakeup timer interrupt period)                              | 39              |

|          | Counting Condition (only for the models with the /RST output function)   | 39              |

|          | Wakeup Timer Setting Procedure                                           |                 |

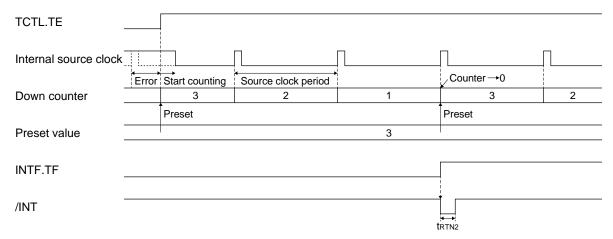

|          | Starting Count                                                           |                 |

|          | Reading Counter Data                                                     |                 |

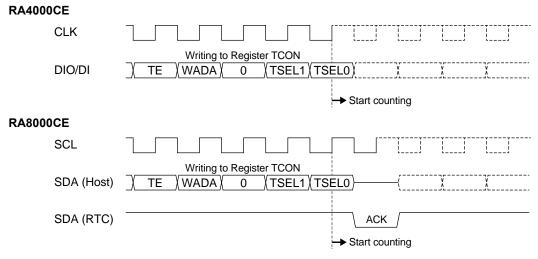

|          | Resetting Counter                                                        |                 |

|          | Wakeup Timer Interrupt                                                   |                 |

| 3.8 FO   | UT Output Function                                                       | 45              |

| 3.8.1    | Overview                                                                 |                 |

| 3.8.2    | Operations                                                               | 45              |

|          | Initial Settings                                                         |                 |

|          | Controlling FOUT Output (when not using the FOE pin)                     |                 |

|          | Controlling FOUT Output (when using the FOE pin)                         |                 |

|          | Wakeup Timer Interrupt Signal Output from FOUT pin                       |                 |

|          | set Output Function                                                      |                 |

|          | Overview                                                                 |                 |

| 3.9.2    | Operations  V <sub>DD</sub> Voltage Detection Operation for Reset Output |                 |

|          | Reset Output Flag                                                        | 47              |

|          | I/O Control During Reset Output                                          |                 |

| 3.10 Sel | If-Monitoring Function                                                   |                 |

|          | Overview                                                                 |                 |

|          | Self-Monitoring Flags                                                    |                 |

|          | Power-On Reset Detection: PORF flag                                      | 48              |

|          | Crystal Oscillation Stop Detection: OSCSTPF flag                         | 48              |

|          | Invalid Date and Time Data Warning: VLF Flag                             |                 |

| 2 40 0   | Temperature Compensation Update Stop Detection: VTMPLF flag              |                 |

|          | Self-Monitoring Flag Output Function                                     | 48<br><b>40</b> |

| 4 77 IIM | no Stamp SUPOTION                                                        | 70              |

|   |       |      | Overview                                                         |      |

|---|-------|------|------------------------------------------------------------------|------|

|   | 3.1   | 1.2  | Time Stamp Triggers                                              |      |

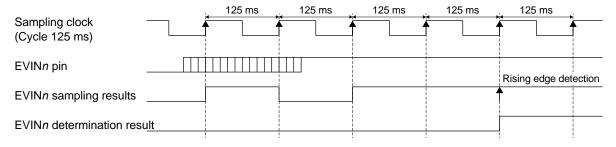

|   |       |      | External Event Inputs (EVINn pin) Trigger                        |      |

|   |       |      | Internal Event Trigger                                           |      |

|   | 2.4   | 1 2  | Command trigger                                                  |      |

|   | ا . ا | 1.3  | Time Stamp Buffer                                                |      |

|   |       |      | Time Stamp Data Time Stamp Buffer Operating Mode                 |      |

|   |       |      | Time Stamp Buffer Write Mode                                     |      |

|   | 3 1   | 1 4  | Operations                                                       |      |

|   | 0.1   | •••  | Initial Settings                                                 |      |

|   |       |      | Time Stamp Capturing Operation                                   |      |

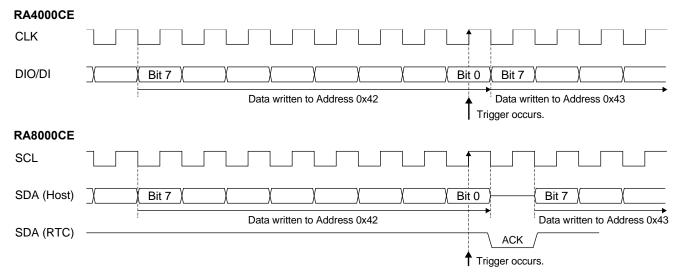

|   |       |      | Issuing Command Trigger                                          |      |

|   |       |      | Reading Time Stamp Data                                          |      |

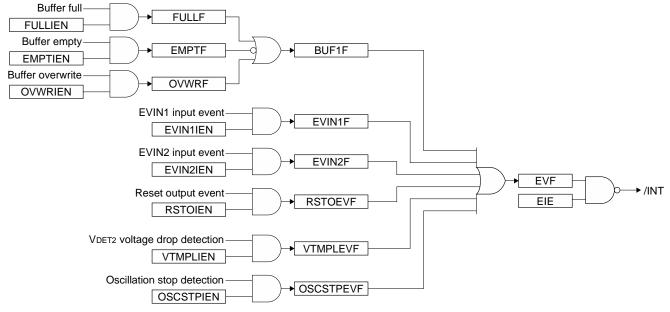

|   |       |      | Time Stamp (Event Detection) Interrupts                          | . 62 |

|   | 3.1   | 1.6  | Reading/Writing in SRAM Mode                                     | . 63 |

|   | 3 12  | SO   | UT Output Function                                               | 64   |

|   | •     |      | Status Output                                                    |      |

|   |       |      | DC Output                                                        |      |

|   | _     |      | ·                                                                |      |

| 4 | Ke    | gist | ers                                                              | .65  |

|   | 4.1   | List | of Registers                                                     | . 65 |

|   |       |      | Symbol meanings                                                  |      |

|   |       |      | Bank 0                                                           |      |

|   |       |      | Bank 1                                                           |      |

|   |       |      | Bank 2                                                           |      |

|   |       |      | Bank 3                                                           |      |

|   |       |      | Bank 4                                                           |      |

|   |       |      | Bank 6/7 (when reading time stamp (BCD) data in Direct mode)     |      |

|   |       |      | Bank 6/7 (when reading time stamp data (BIN) in Direct mode)     |      |

|   |       |      | Bank 6 (SRAM mode)                                               | . 69 |

|   | 4.2   | Doc  | scription of Registers                                           |      |

|   | 4.2   | Des  | 0x00: SEC (Second Data) [BCD mode]                               |      |

|   |       |      | 0x01: MIN (Minute Data) [BCD mode]                               |      |

|   |       |      | 0x02: HOUR (Hour Data) [BCD mode]                                |      |

|   |       |      | 0x03: WEEKDAY (Day-of-Week Data) [BCD mode]                      | . 70 |

|   |       |      | 0x04: DAY (Day Data) [BCD mode]                                  | . 71 |

|   |       |      | 0x05: MONTH (Month Data) [BCD mode]                              | . 71 |

|   |       |      | 0x06: YEAR (Year Data) [BCD mode]                                |      |

|   |       |      | 0x07: ALM_MIN (Minute Alarm) [BCD mode]                          |      |

|   |       |      | 0x08: ALM_HOUR (Hour Alarm) [BCD mode]                           |      |

|   |       |      | 0x09: ALM_WEEKDAY (Day-of-Week Alarm / Day Alarm) [BCD mode]     |      |

|   |       |      | 0x0B: WTCNT M (Wakeup Timer Counter Middle)                      |      |

|   |       |      | 0x0C: WTCNT_H (Wakeup Timer Counter High)                        |      |

|   |       |      | 0x0D: TCTL (Timer Control)                                       |      |

|   |       |      | 0x0E: INTF (Status Flag)                                         | .75  |

|   |       |      | 0x0F: TSTP_INTE (Timer Stop and Interrupt Enable)                |      |

|   |       |      | 0x10: SUBSEC_L (Sub-Second Data Low)                             |      |

|   |       |      | 0x11: SUBSEC_H (Sub-Second Data High)                            |      |

|   |       |      | 0x12: SEC_MIR (Mirrored Second Data, = 0x00) [BCD mode]          | . 78 |

|   |       |      | 0x13: MIN_MIR (Mirrored Minute Data, = 0x0h) [BCD mode]          |      |

|   |       |      | 0x14: HOUR_MIR (Mirrored Hour Data, = 0x02) [BCD mode]           |      |

|   |       |      | 0x15: WEEKDAY_MIR (Mirrored Day-of-Week Data, = 0x03) [BCD mode] |      |

|   |       |      | 0x16: DAY_MIR (Mirrored Day Data, = 0x04) [BCD mode]             |      |

|   |       |      | 0x18: YEAR_MIR (Mirrored Year Data, = 0x06) [BCD mode]           |      |

|   |       |      | 0x12: SEC_BIN0 (Second Binary Data 0) [BIN mode]                 |      |

|   |       |      | 0x13: SEC_BIN1 (Second Binary Data 1) [BIN mode]                 |      |

|   |       |      | 0x14: SEC_BIN2 (Second Binary Data 2) [BIN mode]                 |      |

|   |       |      |                                                                  |      |

|                 | 0x15: SEC_BIN3 (Second Binary Data 3) [BIN mode]                                                   |          |

|-----------------|----------------------------------------------------------------------------------------------------|----------|

|                 | 0x16: SEC_BIN4 (Second Binary Data 4) [BIN mode]                                                   |          |

|                 | 0x19: OFS_SUBSEC_H (Offset Sub-Second Data High)                                                   |          |

|                 | 0x1A: OFS_SUBSEC_L (Offset Sub-Second Data Low)                                                    |          |

|                 | 0x1B: DIG_TRIM_H (Digital Trimming Data High)<br>0x1C: DIG_TRIM_L (Digital Trimming Data Low)      |          |

|                 | 0x1C: DIG_1RIM_E (Digital Triffilling Data Low)<br>0x1D: TCTL_MIR (Mirrored Timer Control, = 0x0D) |          |

|                 | 0x1E: INTF_MIR (Mirrored Status Flag, = 0x0E)                                                      |          |

|                 | 0x1F: CNTSEL (Counter Select)                                                                      |          |

|                 | 0x20: EVIN EN (Event Input Enable)                                                                 |          |

|                 | 0x21: EVIN1_CFG (EVIN1 Configuration)                                                              |          |

|                 | 0x23: EVIN2_CFG (EVIN2 Configuration)                                                              |          |

|                 | 0x22: EVIN1_FLT (EVIN1 Noise Filter)                                                               |          |

|                 | 0x24: EVIN2_FLT (EVIN2 Noise Filter)                                                               |          |

|                 | 0x27: BUF1_CFG1 (BUF1 Configuration 1)                                                             |          |

|                 | 0x28: BUF1_STAT (BUF1 Status)                                                                      |          |

|                 | 0x29: BUF1_CFG2 (BUF1 Configuration 2)                                                             |          |

|                 | 0x30: ALM_SEC (Second Alarm)<br>0x31: ALM_MIN_MIR (Mirrored Minute Alarm, = 0x07)                  |          |

|                 | 0x31: ALM_MIN_MIR (Mirrored Minute Alarm, = 0x07)                                                  |          |

|                 | 0x33: ALM_WEEKDAY_MIR (Mirrored Day-of-Week Alarm / Day Alarm, = 0x09)                             |          |

|                 | 0x34: UPDISEL (Time Update Interrupt Select)                                                       |          |

|                 | 0x38: WTICFG (Wakeup Timer Interrupt Configuration)                                                |          |

|                 | 0x39: WTCTL (Wakeup Timer Control)                                                                 |          |

|                 | 0x3A: WTCNT_L_MIR (Mirrored Wakeup Timer Counter Low, = 0x0A)                                      |          |

|                 | 0x3B: WTCNT_M_MIR (Mirrored Wakeup Timer Counter Middle, = 0x0B)                                   |          |

|                 | 0x3C: WTCNT_H_MIR (Mirrored Wakeup Timer Counter High, = 0x0C)                                     |          |

|                 | 0x3D: TCTL_MIR (Mirrored Timer Control, = 0x0D)                                                    |          |

|                 | 0x3E: INTF_MIR (Mirrored Status Flag, = 0x0E)                                                      |          |

|                 | 0x3F: TSTP_INTE_MIR (Mirrored Timer Stop and Interrupt Enable, = 0x0F)                             |          |

|                 | 0x41: WRCMD_CFG (Write Command Configuration)                                                      | 09       |

|                 | 0x43: EVNT_INTE (Event Interrupt Enable)                                                           | 90<br>an |

|                 | 0x44: CAP_EN (Capture Enable)                                                                      |          |

|                 | 0x45: INTF MIR (Mirrored Status Flag, = 0x0E)                                                      | 91       |

|                 | 0x46: BUF_INTF (Buffer Interrupt Factor)                                                           |          |

|                 | 0x47: EVNT_INTÈ (Event Interrupt Factor)                                                           |          |

|                 | 0x51: EVIN1_EVCNT (EVIN1 Event Counter)                                                            | 93       |

|                 | 0x52: EVIN2_EVCNT (EVIN2 Event Counter)                                                            | 93       |

|                 | 0x54: EVINMON (EVIN Monitor)                                                                       |          |

|                 | 0x55: SOUTCTL (SOUT Control)                                                                       | 93       |

| 5 El            | ectrical Characteristics                                                                           | 95       |

|                 | Absolute Maximum Ratings                                                                           |          |

| 5.1             | •                                                                                                  |          |

| 5.2             | Recommended Operating Conditions                                                                   | 95       |

| 5.3             | Frequency Characteristics                                                                          | 95       |

| 5.4             | DC Characteristics                                                                                 |          |

| J. <del>T</del> | DC Characteristics                                                                                 |          |

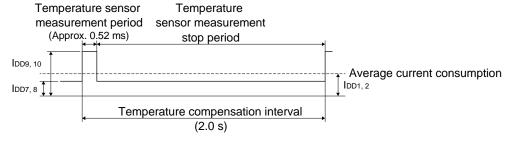

|                 | Temperature Compensation Operation and Current Consumption                                         |          |

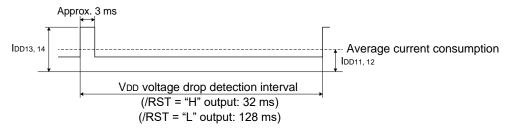

|                 | Current Consumption of Model with /RST Output Pin                                                  |          |

|                 | Detection Voltages for State Transition and Self-Monitoring Functions                              | 97       |

| 5.5             | AC Characteristics                                                                                 |          |

| J.J             | RA4000CE AC Characteristics                                                                        |          |

|                 | RA8000CE AC Characteristics                                                                        |          |

| 5.6             | Power-On Characteristics                                                                           |          |

|                 |                                                                                                    |          |

| 5.7             | Reset Output Characteristics                                                                       | 101      |

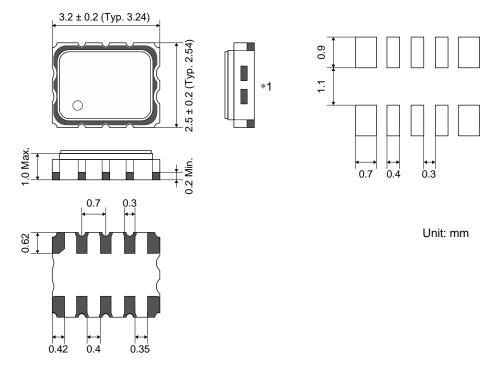

| 6 Pa            | ackage                                                                                             | 102      |

|                 | _                                                                                                  |          |

| 6.1             | Package Dimensions                                                                                 | 102      |

ETM64E-02

| 6   | 3.2  | Marking Layout                                                     | 102 |

|-----|------|--------------------------------------------------------------------|-----|

| 7   | No   | tes on Mounting                                                    | 103 |

|     |      | Static Electricity                                                 |     |

|     |      | Noise                                                              |     |

|     |      | Input Voltage                                                      |     |

|     |      | Handling of Unused Pins                                            |     |

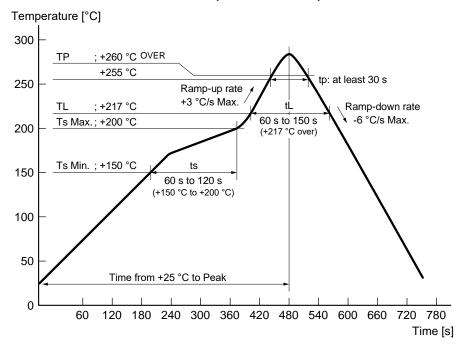

|     |      | Soldering Temperature                                              |     |

|     |      | Mounting Equipment                                                 |     |

|     |      | Ultrasonic Cleaning                                                |     |

|     |      | Mounting OrientationLeakage between Pins                           |     |

|     |      | Solder Heat Resistance Evaluation Profile (for reference)          |     |

| 8   | Мо   | sisture Resistance/Electrostatic Breakdown Voltage Characteristics | 105 |

| 8   | 3.1  | Moisture Sensitivity Level (MSL)                                   | 105 |

| 8   | 3.2  | Electrostatic Breakdown Voltage                                    | 105 |

| 9   | Sa   | mple Connection Diagram                                            | 106 |

| 10  | Pa   | cking Information (reference)                                      | 108 |

| . • |      | Taping Specification (TE0804L)                                     |     |

|     |      | Reel Specification                                                 |     |

| Lis | st o | f Figures/Tables                                                   | 109 |

|     |      | Figures                                                            |     |

|     |      | Tables                                                             | 110 |

# 1 Overview

The RA4000CE/RA8000CE is a real-time clock module with integrated 32.768 kHz digital temperature compensated crystal oscillator (DTCXO) and conforms to the AEC-Q100 compliant. It includes various functions such as a second-to-year clock/calendar with a leap-year correction, time alarm, wakeup timer, time update interrupts, clock output, and a time stamp function that can record two times and dates when an external or internal event occurs, and the power supply statuses that have been detected by the self-monitoring function. This product is capable of low power operation and conforms to the AEC-Q100 compliant, thus it is usable for on-vehicle applications as well as various time keeping applications.

RA4000CE YB A 0 1) 2 34

- ① Model CE type package 3.2 x 2.5 x 1.0 mm

- 2 Frequency tolerance

- 3 Pin Option

- A: Option A-E

- 4 Reset output function

- 0: No /RST pin

- 8: With /RST pin (VDD drop detection voltage: +2.4 V Typ.)

Table 1.1 Product Lineup

| Product name         | Interface            | Frequency accuracy *1 | External event input (EVINn) | Reset output<br>(/RST) | Clock output<br>(FOUT or<br>/INT) | FOUT enable<br>(FOE) | Status<br>output<br>(SOUT) |

|----------------------|----------------------|-----------------------|------------------------------|------------------------|-----------------------------------|----------------------|----------------------------|

| RA4000CE Option A YB |                      | YB                    | 2 inputs                     | _                      | 1                                 | _                    | _                          |

| RA4000CE Option B YB | 3-wire SPI           | YB                    | 2 inputs                     | ✓                      | 1                                 | _                    | _                          |

| RA4000CE Option C YB |                      | YB                    | _                            | _                      | 1                                 | _                    | _                          |

| RA4000CE Option D YB | 4 voine CDI          | YB                    | 1 input                      | _                      | 1                                 | _                    | ✓                          |

| RA4000CE Option E YB | 4-wire SPI           | YB                    | 1 input                      | ✓                      | 1                                 | _                    | ✓                          |

| RA8000CE Option A YB |                      | YB                    | 2 inputs                     | _                      | 1                                 | _                    | ✓                          |

| RA8000CE Option B YB | 12C D                | YB                    | 2 inputs                     | ✓                      | 1                                 | _                    | ✓                          |

| RA8000CE Option C YB | I <sup>2</sup> C-Bus | YB                    | _                            | _                      | 1                                 | _                    | _                          |

| RA8000CE Option D YB |                      | YB                    | 1 input                      | _                      | 1                                 | 1                    | /                          |

<sup>✓:</sup> Available, –: Unavailable

Table 1.2 Features

| Produc         | t lineup       | RA4000CE                                                                                  | RA8000CE                                                                                                       |  |  |  |  |  |  |

|----------------|----------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Host interface |                | 3-wire SPI or 4-wire SPI *1                                                               | I <sup>2</sup> C-Bus *1                                                                                        |  |  |  |  |  |  |

| Crystal        | oscillator     | A 32.768 kHz digital temperature compensations                                            | ated crystal oscillator (DTCXO) is included.                                                                   |  |  |  |  |  |  |

| Clock/c        | alendar        | counter are included. [BCD mode]                                                          |                                                                                                                |  |  |  |  |  |  |

|                |                | A binary counter for counting 1/1024 second                                               |                                                                                                                |  |  |  |  |  |  |

|                |                | A binary counter for counting seconds such                                                |                                                                                                                |  |  |  |  |  |  |

|                |                | <ul> <li>An automatic leap year correction function i<br/>provided. [BCD mode]</li> </ul> | s included and a leap second correction method is                                                              |  |  |  |  |  |  |

|                |                | Time update interrupts can be generated. ( [BCD mode]                                     | • Time update interrupts can be generated. (1-second, 1-minute, or 1-hour counter update intervals) [BCD model |  |  |  |  |  |  |

|                |                | <ul> <li>A theoretical regulation function is included.</li> </ul>                        | A theoretical regulation function is included.                                                                 |  |  |  |  |  |  |

| Wakeup         | timer          | • Can generate an interrupt in 976.56 µs to 3                                             | • Can generate an interrupt in 976.56 µs to 32-year cycle.                                                     |  |  |  |  |  |  |

|                |                | Can be used as a time integration meter.                                                  |                                                                                                                |  |  |  |  |  |  |

|                |                | <ul> <li>Can be used as a watchdog timer.</li> </ul>                                      |                                                                                                                |  |  |  |  |  |  |

|                |                | Can be used as a universal counter for coult                                              | Can be used as a universal counter for counting EVIN2 pin inputs (external event inputs).                      |  |  |  |  |  |  |

| Alarm          |                | Can generate an interrupt at the specified day (                                          | or day of the week), hour, minute, and second. [BCD mode]                                                      |  |  |  |  |  |  |

| Time           | Trigger source | External event (EVINn) input *1                                                           |                                                                                                                |  |  |  |  |  |  |

| stamp          |                | Voltage drop detection/oscillation stop detection                                         | ction                                                                                                          |  |  |  |  |  |  |

|                |                | Command input from the host                                                               |                                                                                                                |  |  |  |  |  |  |

|                | Record data    | 1/1024-second data                                                                        | • 1/1024-second data                                                                                           |  |  |  |  |  |  |

|                |                | Time data (seconds, minutes, hours, days, m                                               | Time data (seconds, minutes, hours, days, months, and years [BCD mode] or binary time [BIN mode])              |  |  |  |  |  |  |

|                |                | Trigger source                                                                            |                                                                                                                |  |  |  |  |  |  |

|                |                | Internal status                                                                           |                                                                                                                |  |  |  |  |  |  |

<sup>\*1</sup> For the accuracy (YB), refer to the frequency tolerance shown in "5.3 Frequency Characteristics."

| Product lineup                       | RA4000CE                                                      | RA8000CE                                                 |

|--------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|

| Number of recordable events          | Two events                                                    |                                                          |

| Clock output (FOUT) *1               | Selectable from 32.768 kHz, 1024 Hz, and 1 Hz                 | outputs                                                  |

|                                      | Output can be controlled by a register.                       |                                                          |

| Status output (SOUT) *1              | Can output the selected internal flag (interrupt flag         | , voltage drop detection flag) status.                   |

| Reset output *1                      | Can output a reset signal when a V <sub>DD</sub> voltage drop | status is detected.                                      |

| Self-monitoring function             | Can generate an interrupt when the oscillation stop           | os or a V <sub>DD</sub> voltage drop status is detected. |

| Operating voltage (V <sub>DD</sub> ) | 1.60 V to 5.5 V                                               |                                                          |

| Operating temperature                | -40 °C to +125 °C                                             |                                                          |

<sup>\*1</sup> See Table 1.1.

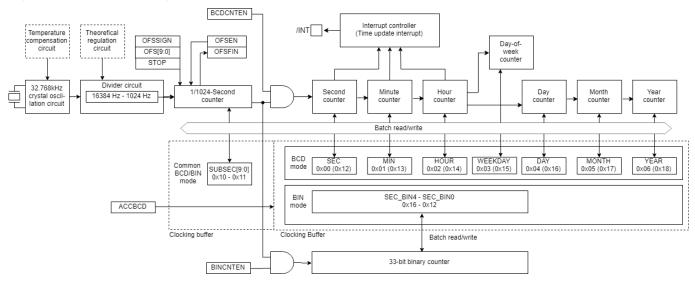

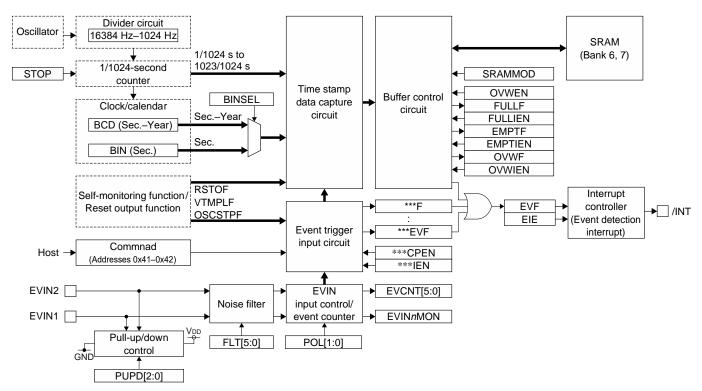

# 1.1 Block Diagram

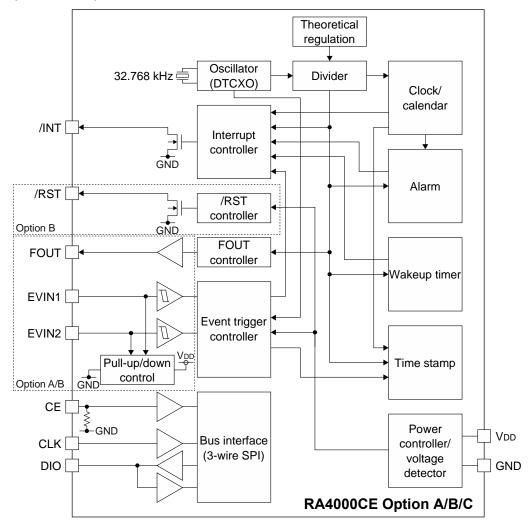

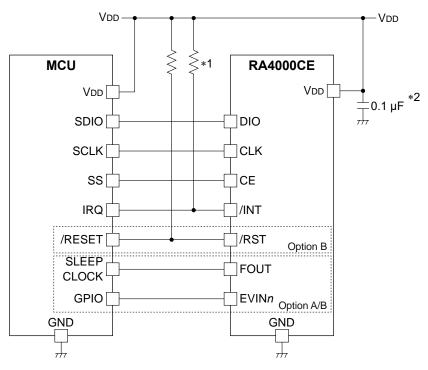

# RA4000CE (3-wire SPI)

Figure 1.1 RA4000CE Option A/B/C Block Diagram

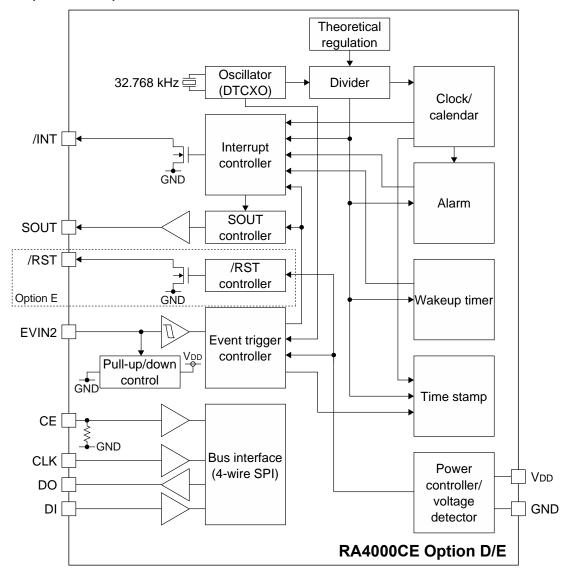

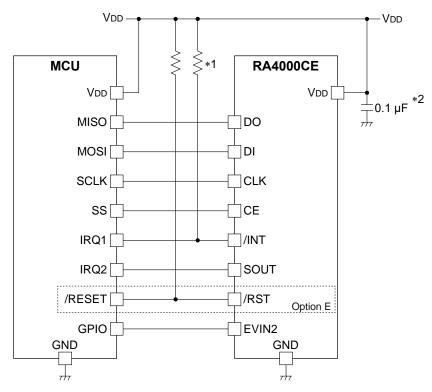

# RA4000CE (4-wire SPI)

Figure 1.2 RA4000CE Option D/E Block Diagram

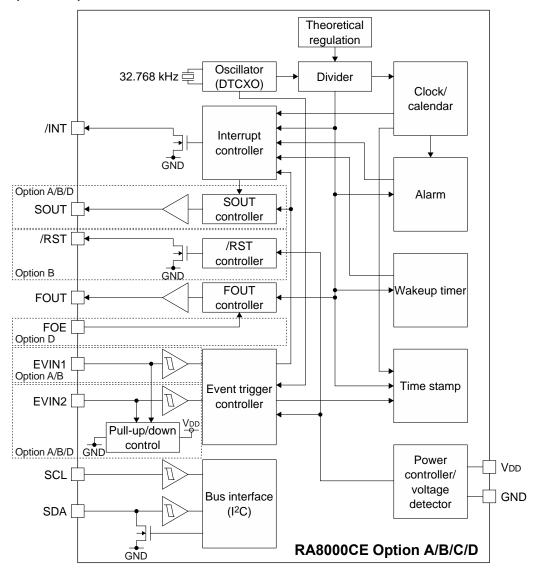

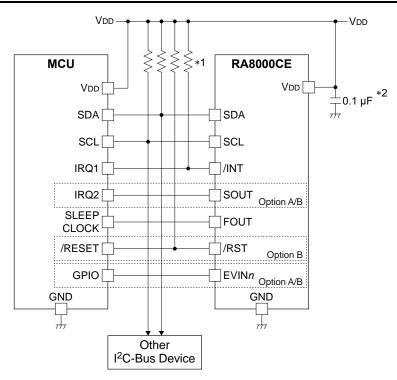

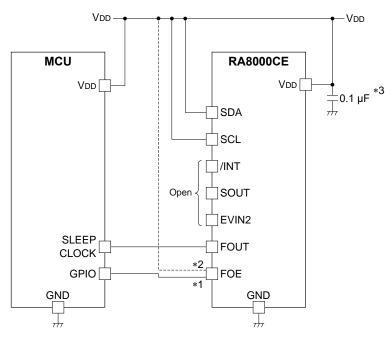

# RA8000CE (I<sup>2</sup>C-Bus)

Figure 1.3 RA8000CE Option A/B/C/D Block Diagram

#### 1.2 Pin

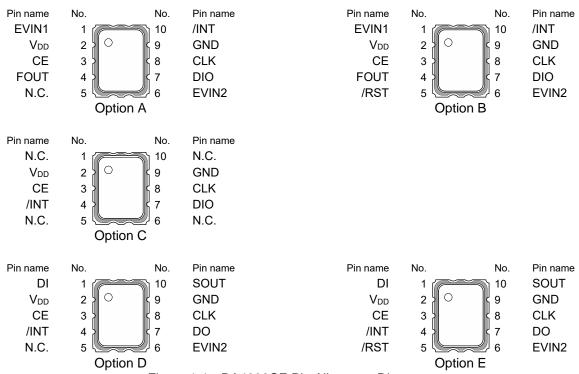

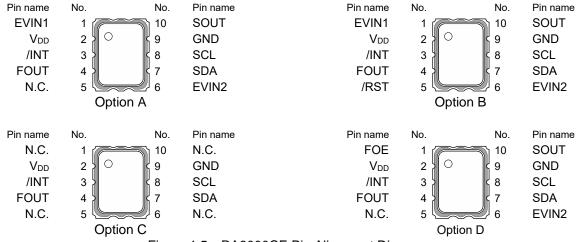

# 1.2.1 Pin Alignment Diagram

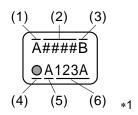

#### RA4000CE

Figure 1.4 RA4000CE Pin Alignment Diagrams

#### **RA8000CE**

Figure 1.5 RA8000CE Pin Alignment Diagrams

<sup>\*</sup> The N.C. pins (Pins 1, 5, and 6) of the models in Option A, C, or D are always pulled down with a built-in pull-down resister. Therefore, these pins should be left open (do not electrically connect anything).

# 1.2.2 Pin Descriptions

# **Symbol Meanings**

I/O I: Input pin

O: Output pin I/O: Input/output pin

Initial state Hi-Z: High impedance

PU: Pulled up

PD: Pulled down

Model-specific column ✓: Available

-: Unavailable

Table 1.3 Pin Descriptions

| Pin   | 1/0 | I/O Initial Function |                                                                                                                                                                                                                                                                                                                                                                                     |   | RA | 4000 | CE |   | RA8000CE |          |   |          |  |

|-------|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------|----|---|----------|----------|---|----------|--|

| name  | 1/0 | state                | Function                                                                                                                                                                                                                                                                                                                                                                            | Α | В  | С    | D  | Е | Α        | В        | С | D        |  |

| EVIN1 | ı   | PU<br>(1 MΩ)         | External event input pins These pins are used to input time stamp trigger signals (detectable even                                                                                                                                                                                                                                                                                  | 1 | 1  | -    | -  | _ | 1        | 1        | _ | -        |  |

| EVIN2 | -   |                      | in reset output state (Safe mode)).  Programmable pull-up and pull-down resistors and noise filters are included.                                                                                                                                                                                                                                                                   | 1 | 1  | -    | 1  | 1 | 1        | 1        | _ | 1        |  |

| CLK   | I   | Hi-Z                 | 3-wire/4-wire SPI serial clock input pin In Normal mode, placing this pin into a floating state is not allowed. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed.                                                                                                                                                 |   | 1  | 1    | 1  | 1 | _        | _        | _ | _        |  |

| DIO   | I/O | Hi-Z                 | 3-wire SPI serial data input/output pin In Normal mode and when this pin is in input state, placing this pin into a floating state is not allowed. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed.                                                                                                              | 1 | 1  | 1    | _  | _ | _        | _        | - | _        |  |

| DO    | 0   | Hi-Z                 | 4-wire SPI serial data output pin In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to output and set into a Hi-Z state.                                                                                                                                                                                                                                      | - | -  | -    | 1  | ✓ | _        | _        | _ | _        |  |

| DI    | I   | Hi-Z                 | 4-wire SPI serial data input pin In Normal mode, placing this pin into a floating state is not allowed. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed.                                                                                                                                                         | _ | _  | _    | 1  | 1 | _        | _        | _ | _        |  |

| CE    | I   | PD<br>(300 kΩ)       | 3-wire/4-wire SPI slave select input pin A pull-down resistor is included. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed.                                                                                                                                                                                      | • | 1  | 1    | 1  | 1 | _        | _        | _ | _        |  |

| SCL   | I   | Hi-Z                 | I <sup>2</sup> C-Bus serial clock input pin In Normal mode, placing this pin into a floating state is not allowed. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed. This pin can be externally pulled up to a voltage up to 5.5 V.                                                                               |   | _  | _    | _  | _ | 1        | 1        | 1 | <b>✓</b> |  |

| SDA   | I/O | Hi-Z                 | I²C-Bus serial data input/output pin (N-ch. open drain) This pin inputs or outputs addresses, data, acknowledgement and other bits in sync with the SCL signal. This pin is an N-ch open drain output and can be externally pulled up to a voltage up to 5.5 V. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed. |   | _  | _    | _  | _ | 1        | 1        | ✓ | ✓        |  |

| FOUT  | 0   | Hi-Z                 | Clock output pin (CMOS) 32.768 kHz, 1024 Hz or 1 Hz clock output is selectable. Can be switched to the wakeup timer interrupt output (CMOS). In Safe mode with the WTICFG.RSTOPT0 bit set to 0, this pin is disabled to output and set into a Hi-Z state.                                                                                                                           | 1 | 1  | _    | _  | _ | 1        | <b>✓</b> | ✓ | ✓        |  |

| FOE   | I   | Hi-Z                 | FOUT output enable input pin When an H level is input, the FOUT pin outputs a square wave with the frequency set by a register. When an L level is input, the FOUT pin is set into a Hi-Z state. In Safe mode with the WTICFG.RSTOPT1 bit set to 0, this pin is disabled to input, thus a floating state is allowed.                                                                |   | _  | _    | _  | _ | _        | _        | _ | ✓        |  |

| Pin                    | I/O    | Initial | Formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | RA       | 4000 | CE |          | RA8000CE |          |   |          |  |

|------------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------|----|----------|----------|----------|---|----------|--|

| name                   | 1/0    | state   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | В        | С    | D  | Е        | Α        | В        | С | D        |  |

| /INT                   | 0      | Hi-Z    | Interrupt output pin (N-ch. open drain) The wakeup timer, time update, alarm, and/or event detection interrupt signals can be selected to output from this pin. When two or more interruptions are selected, they are ORed before being output.(Equal to NOR gate) In Safe mode with the WTICFG.RSTOPT0 bit set to 0, this pin is disabled to output and set into a Hi-Z state. This pin can be externally pulled up to a voltage up to 5.5 V.                                                                                                                                                                                                                                                                                             | ✓ | <b>✓</b> | •    | 1  | <b>✓</b> | ✓        | <b>√</b> | ✓ | <b>✓</b> |  |

| SOUT                   | 0      | Hi-Z    | Status output pin One of the internal flags (TF/AF/UF/EF/VTMPLF/VLF) can be selected to output its status from this pin. The output signal polarity can also be selected. In Safe mode with the WTICFG.RSTOPT0 bit set to 0, this pin is disabled to output and set into a Hi-Z state.                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - | _        | _    | 1  | <b>✓</b> | <b>√</b> | 1        | - | 1        |  |

| /RST                   | (I) /O | Hi-Z    | Reset output pin (N-ch open drain) A reset signal can be output to external devices when a $V_{\text{DD}}$ voltage drop below the predefined value is detected. When the $V_{\text{DD}}$ voltage is restored (a $V_{\text{DD}}$ voltage rise to the predefined value is detected), the reset output is cancelled (set to a Hi-Z state) after 60 ms from the detection. This pin is an N-ch open drain output. Connect an appropriate pull-up resistor according to the capacity of the signal line. The external pull-up voltage should be the $V_{\text{DD}}$ level of the RTC or higher. When the reset output function is not used in the model with the /RST pin (RA4000CE-B, E, RA8000CE-B), this pin should be fixed at a GND level. | _ | 1        | _    | _  | 1        | _        | ✓        | _ | _        |  |

| <b>V</b> <sub>DD</sub> | -      | _       | Main power supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 | 1        | 1    | 1  | 1        | 1        | 1        | 1 | 1        |  |

| GND                    | -      | _       | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 | 1        | 1    | 1  | 1        | 1        | 1        | 1 | 1        |  |

Notes: • Do not leave the unused input and input/output pins open nor apply an intermediate potential to them if the internal pull-up or -down resistor is not enabled.

- Leave the output pins (FOUT, SOUT, /INT, and DO) open when they are not used.

- When the reset output function is not used in the model with the /RST pin function, the /RST pin should be fixed at a GND level.

- The input pins allow applying a voltage up to 5.5 V regardless of the V<sub>DD</sub> voltage level.

- The /INT output pin can be pulled up to a voltage up to 5.5 V regardless of the V<sub>DD</sub> voltage level.

- The /RST output pin can be pulled up to a voltage within the range from  $V_{DD}$  to 5.5 V.

- Pin 5 of the models without the /RST pin function should be left open, as it outputs an L level.

# 2 Power Supply and Initialization

# 2.1 Power Supply

The table below lists the RA4000CE/RA8000CE power supply pins.

Table 2.1 List of Power Supply Pins

| Pin name | Function              |

|----------|-----------------------|

| $V_{DD}$ | Main power supply pin |

| GND      | Ground pin            |

The RA4000CE/RA8000CE operates with the power supply voltage applied to the  $V_{DD}$  pin. For the operating power supply range, refer to "5.2 Recommended Operating Conditions."

Note: Design the PCB pattern so that a bypass capacitor will be placed as close to the V<sub>DD</sub> pin as possible.

## 2.2 Initialization

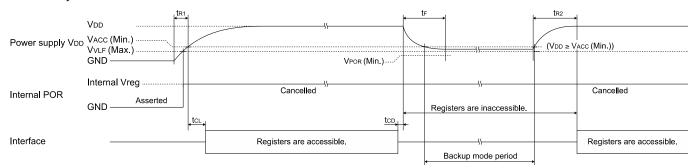

## 2.2.1 Power-On Sequence

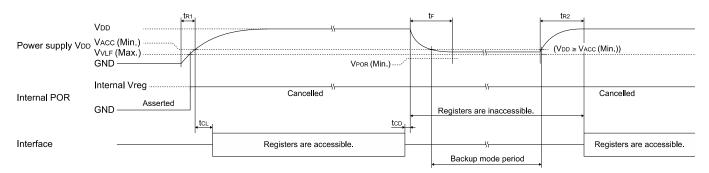

The RA4000CE/RA8000CE executes a power-on reset processing when the  $V_{DD}$  voltage is supplied. To make certain that the RA4000CE/RA8000CE executes a power-on reset, satisfy the power-on specifications ( $t_{R1}$ , refer to "5.6 Power-On Characteristics"). The  $t_{CL}$  in Figure 2.1 shows the time for canceling power-on reset.

Before turning the power supply back on after being turned off, be sure to maintain an OFF period with the  $V_{DD}$  pin set to the GND level for at least 100 ms after turning off. Then turn the power supply back on again with the power supply initial rise time specification satisfied.

(1) In the case of a model without the /RST output function

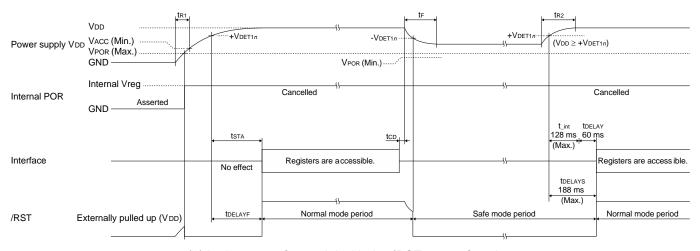

(2) In the case of a model with the /RST output function

Figure 2.1 Power-On Sequence

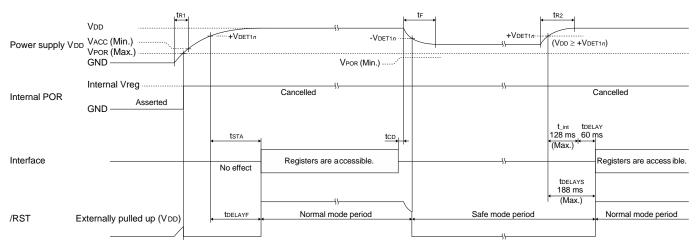

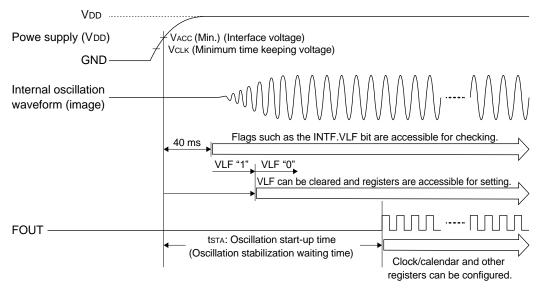

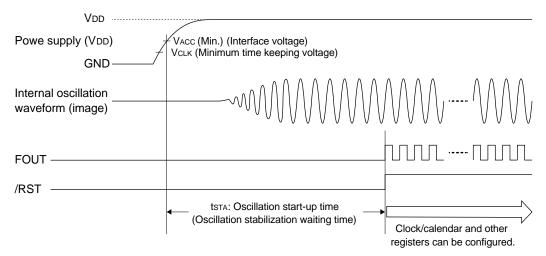

#### 2.2.2 Oscillation Start-UP Time

When the  $V_{DD}$  voltage is applied, the crystal oscillation circuit starts oscillating. The host interface becomes usable after 40 ms from turning  $V_{DD}$  on. However, a wait time is required until the internal crystal oscillation waveform has a sufficient amplitude before the clock/calendar counter value can be set and read. This refers to the oscillation start-up time ( $t_{STA}$ , refer to "5.3 Frequency Characteristics").

There are two methods to secure the wait time in the models without the /RST output function: one is the method for repeatedly trying to clear the INTF.OSCSTPF and INTF.VLF bits, another is the method for waiting by the host until  $t_{STA}$  has elapsed after applying  $V_{DD}$ . The former can shorten the wait time until the clock/calendar counter value will be able to set and read. On the other hand, the latter can set the clock/calendar counter with higher time accuracy, as the crystal oscillation frequency becomes more stable although the wait time becomes longer

The INTF.OSCSTPF and INTF.VLF bits are set to 1 by the oscillation stop detection function immediately after the crystal oscillation circuit starts oscillating. While the oscillation stop status is being detected, these bits cannot be cleared to 0 even if 0 is written to these bits through the host interface. When the oscillation stop status is cancelled by the grown internal oscillation waveform amplitude, the INTF.OSCSTPF and INTF.VLF bits can be cleared. Therefore, try to clear these bits at arbitrary time intervals until they are actually cleared. After that the clock/calendar counter value can be set and read.

Make sure that the INTF.VLF bit has been cleared before the host configures the operational settings of the functions shown below (\*).

On the other hand in the models with the /RST output function, the host interface is disabled until the  $V_{DD}$  voltage rises to  $+V_{DET1n}$  or higher. When  $t_{STA}$  has elapsed as well as the condition of  $V_{DD} \ge +V_{DET1n}$  has been satisfied, the /RST output is cancelled and communication can be established allowing access to all registers.

- \* Functions that should be configured after the INTF.VLF bit is cleared:

- Selecting the multi-function pin functions (WTICFG.PINMUX[1:0] bit settings)

- Setting the required timer functions

- Controlling the FOUT output (TCTL.FSEL[1:0] bit settings)

- Setting the temperature compensation execution interval (TSTP\_INTE.CSEL[1:0] bit settings)

#### (1) In the case of a model without the /RST output function

All the registers can be accessed after  $t_{\text{STA}}$  has elapsed.

(2) In the case of a model with the /RST output function

Figure 2.2 Oscillation Start Sequence

## 2.2.3 Initial Settings

It is necessary to initially set the registers after initial power on or when a supply voltage drop with the INTF.VLF bit set to 1 from 0 has occurred. This section shows an example of initial settings.

#### Initial Setting Procedure (for models without the /RST output function)

- 1. Wait for at least 40 ms after the power is initially turned on.

- 2. Cancelling POR and detecting oscillation start-up (polling of the INTF.VLF bit)

The INTF.VLF bit is set to 1 when a power-on reset is issued due to a power supply voltage drop or an oscillation stop is detected.

- 2.1. Read the INTF.VLF bit and go to Step 3 when the read value = 0. If the INTF.VLF bit = 1, perform Steps 2.2 to 2.4.

- 2.2. Write 0x00 to Register INTF to try and clear the INTF.VLF bit and to clear the interrupt flags.

PORF bit (Power-on reset detection flag)

OSCSTPF bit (Oscillation stop detection flag)

UF bit (Time update interrupt flag)

TF bit (Wakeup timer interrupt flag)

AF bit (Alarm interrupt flag)

EVF bit (Event detection interrupt flag)VLF bit (RTC initialize interrupt flag)

- VTMPLF bit (Temperature compensation update stop interrupt flag)

- 2.3. Take a waiting time.

- 2.4. Return to Step 2.1.

- 3. Disable interrupts/counters. (Write 0x00 to Register TSTP INTE.)

- CSEL[1:0] bits (Temperature sensor measurement operation interval)

UIE bit (Disable time update interrupt)

TIE bit (Disable wakeup timer interrupt)

AIE bit (Disable alarm interrupt)

- EIE bit (Disable event detection interrupt)

- STOP bit (Stop counters)

4. Set the current time.

For more information, refer to "3.2 Clock and Calendar Function."

5. Set alarm.

For more information, refer to "3.6 Alarm Function."

6. Set wakeup timer.

For more information, refer to "3.7 Wakeup Timer Function."

RA4000CE/RA8000CE Jump to Top / Bottom

#### Initial Setting Procedure (for models with the /RST output function)

- 1. Wait for at least t<sub>STA</sub> after the power is initially turned on. Or confirm that the /RST output is cancelled.

- Cancelling POR and detecting oscillation start-up (polling of the INTF.VLF bit) The INTF.VLF bit is set to 1 when a power-on reset is issued due to a power supply voltage drop or an oscillation stop is detected.

- Read the INTF.VLF bit and go to Step 3 when the read value = 0. If the INTF.VLF bit = 1, perform Steps 2.2 to 2.4.

- 2.2. Write 0x00 to Register INTF to try and clear the INTF.VLF bit and clearing the interrupt flags.

- PORF bit (Power-on reset detection flag) - OSCSTPF bit (Oscillation stop detection flag) - UF bit (Time update interrupt flag) - TF bit (Wakeup timer interrupt flag) - AF bit (Alarm interrupt flag)

- EVF bit (Event detection interrupt flag) - VLF bit (RTC initialize interrupt flag)

- VTMPLF bit (Temperature compensation update stop interrupt flag)

- 2.3. Take a waiting time.

- 2.4. Return to Step 2.1.

- Disable interrupts/counters. (Write 0x00 to Register TSTP INTE.)

(Temperature sensor measurement operation interval) - CSEL[1:0] bits

- UIE bit (Disable time update interrupt) - TIE bit (Disable wakeup timer interrupt) - AIE bit (Disable alarm interrupt)

- EIE bit (Disable event detection interrupt)

- STOP bit (Stop counters)

Set the current time.

For more information, refer to "3.2 Clock and Calendar Function."

5.

For more information, refer to "3.6 Alarm Function."

6. Set wakeup timer.

For more information, refer to "3.7 Wakeup Timer Function."

RA4000CE/RA8000CE Jump to Top / Bottom

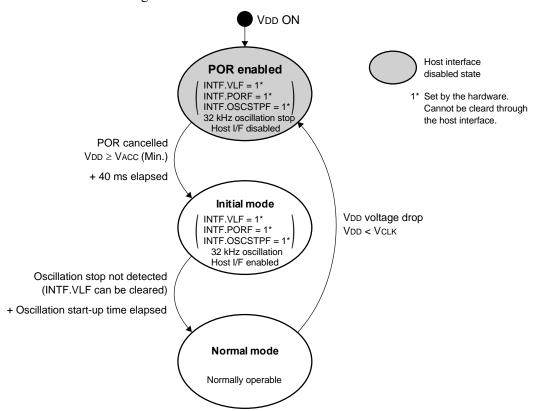

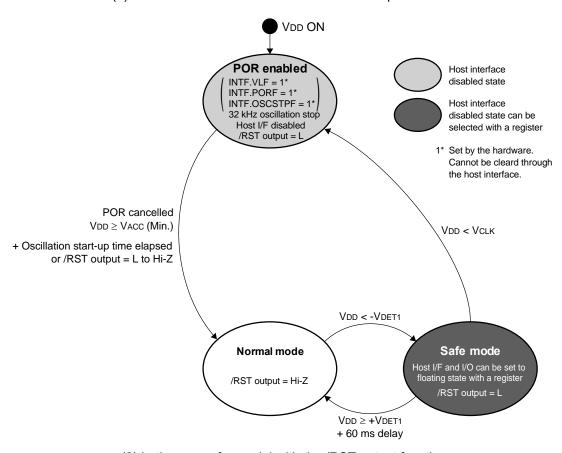

# 2.3 Operating Mode

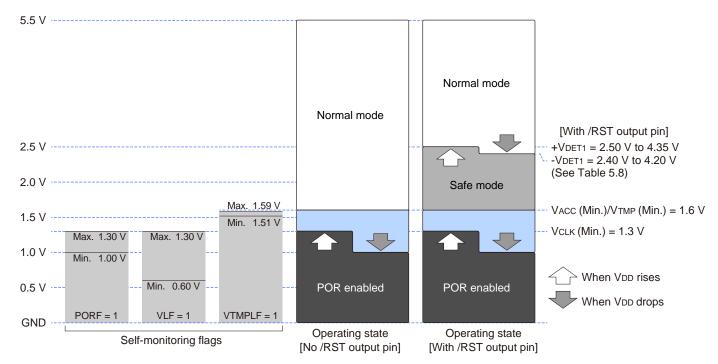

Figure 2.3 shows the state transition diagram of the RA4000CE/RA8000CE.

(1) In the case of a model without the /RST output function

(2) In the case of a model with the /RST output function

Figure 2.3 State Transition Diagram

#### POR enabled

The RA4000CE/RA8000CE is in a reset state. It cannot be accessed by the host.

POR is enabled and the INTF.VLF bit is set to 1.

When the operating mode has transited from Normal or Safe mode described later to this mode due to a V<sub>DD</sub> voltage drop below V<sub>CLK</sub>, POR (Power-On Reset) is executed. In this case, the internal crystal oscillator operation and holding clock/calendar and other data into registers are not guaranteed. If the INTF.VLF bit is set to 1 while operating in Normal mode, it is necessary to initially set the registers again after POR has been cancelled and VLF is cleared in Initial mode.

#### Initial mode

This is an oscillation start-up state after POR has been cancelled and it transits to Normal mode when the oscillation starting operation has completed. Whether transition to Normal mode has completed or not can be determined by checking that the oscillation stop detection result has changed to a non-detected state and the INTF.VLF bit could be cleared to 0.

#### Normal mode

The RA4000CE/RA8000CE is in a normal operating state. The host can access the RA4000CE/RA8000CE registers including the clock/calendar counters.

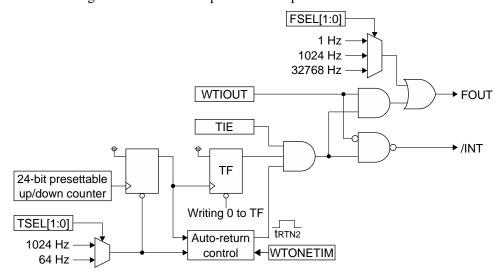

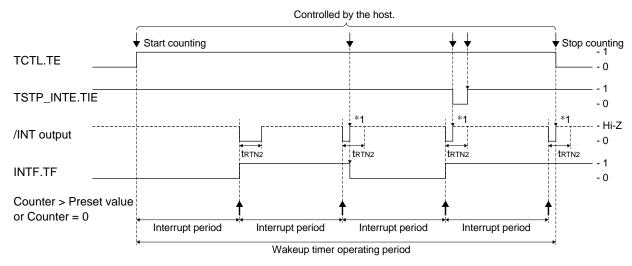

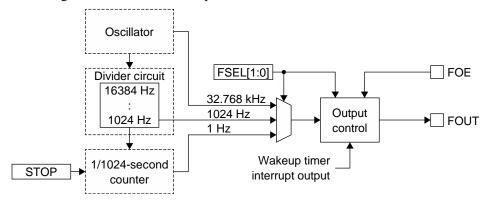

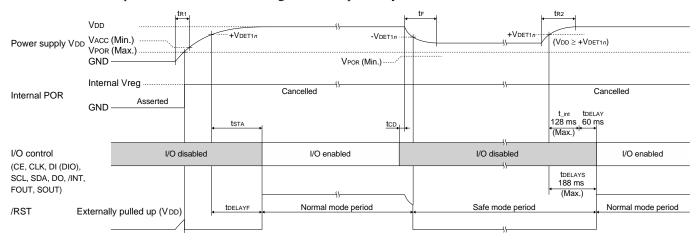

#### Safe mode