# アプリケーションマニュアル

# Real Time Clock Module RX4901CE/RX8901CE

| 製品名称           | 製品型番            |

|----------------|-----------------|

| RX4901CE XS A0 | X1B000471000115 |

| RX4901CE XB A0 | X1B000471000215 |

| RX4901CE XS B0 | X1B000471000315 |

| RX4901CE XB B0 | X1B000471000415 |

| RX4901CE XS C0 | X1B000471000515 |

| RX4901CE XB C0 | X1B000471000615 |

| RX4901CE XS D0 | X1B000471000715 |

| RX4901CE XB D0 | X1B000471000815 |

| RX8901CE XS A0 | X1B000481000115 |

| RX8901CE XB A0 | X1B000481000215 |

| RX8901CE XS B0 | X1B000481000315 |

| RX8901CE XB B0 | X1B000481000415 |

本マニュアルのご使用につきましては、次の点にご留意願います。

- 1. 本資料の内容については、予告無く変更することがあります。弊社製品のご購入およびご使用にあたりましては事前に弊社営業窓口で最新の情報をご確認いただきますとともに、弊社ホームページなどを通じて公開される最新情報に常にご注意ください。

- 2. 本資料の一部または全部を、弊社に無断で転載または複製など他の目的に使用することは堅くお断りします。

- 3. 本資料に掲載されている応用回路、プログラム、使用方法などはあくまでも参考情報であり、これらに起因する第三者の知的財権およびその他の権利侵害ならびに損害の発生に対し、弊社はいかなる保証を行うものではありません。また、本資料によって第三者または弊社の知的財産権およびその他の権利の実施権の許諾を行うものではありません。

- 4. 弊社製品のご使用にあたりましては、弊社製品の誤作動や故障により生命・身体に危害を及ぼすことまたは財産が侵害されることのないように、お客様の責任において、お客様のハードウェア、ソフトウェア、システムに必要な安全設計を行うようお願いします。

- なお、設計および使用に際しては、弊社製品に関する最新の情報 (本資料、仕様書、データシート、マニュアル、弊社ホームページなど) をご確認いただき、それに従ってください。また、上記資料などに掲載されている製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価を行い、お客様の責任において適用可否の判断をお願いします。

- 5. 弊社は正確さを期すために慎重に本資料を作成しておりますが、本資料に掲載されている情報に誤りがないことを保証するものではありません。万一、本資料に掲載されている情報の誤りによってお客様に損害が生じた場合においても、弊社は一切その責任を負いかねます。

- 6. 弊社製品の分解、解析、リバースエンジニアリング、改造、改変、翻案、複製などは堅くお断りします。

- 7. 弊社製品は、一般電子機器製品用途および弊社指定用途に使用されることを意図して設計、開発、製造しています (指定用途)。この指定 用途の範囲を超えて、特別または高度な品質、信頼性が要求され、その誤動作や故障により生命・身体に危害を及ぼす恐れ、膨大な財物損 害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある以下を含む用途 (特定用途) に使用されることを意図していません。

#### 【特定用途】

宇宙機器 (人工衛星・ロケットなど)/ 輸送車両並びにその制御機器 (自動車・航空機・列車・船舶など)

医療機器 / 海底中継機器 / 発電所制御機器/防災·防犯装置 / 交通用機器 / 金融関連機器

上記と同等の信頼性を必要とする用途

お客様に置かれましては、製品を指定用途に限定して使用されることを強く推奨いたします。もし指定用途以外の用途で製品のご使用およびご購入を希望される場合、弊社はお客様の特定用途に弊社製品を使用されることへの商品性、適合性、安全性について、明示的・黙示的に関わらず、いかなる保証をおこなうものではありません。お客様が特定用途での弊社製品の使用を希望される場合は、弊社営業窓口まで事前にご連絡ください。

- 8. 本資料に掲載されている弊社製品および弊社技術を国内外の法令および規制により製造・使用・販売が禁止されている機器・システムに使用することはできません。また、弊社製品および弊社技術を大量破壊兵器等の開発目的、および軍事利用の目的、その他軍事用途等に使用しないでください。弊社製品または弊社技術を輸出または海外に提供する場合は、「外国為替及び外国為替法」、「米国輸出管理規則(EAR)」、その他輸出関連法令を遵守し、係る法令の定めるところにより必要な手続きを行ってください。

- 9. 弊社は、お客様が本資料に掲載されている諸条件に反したことに起因して生じたいかなる損害 (直接・間接を問わず) に関して、一切その 責任を負いかねます。また、お客様が弊社製品を第三者に譲渡、貸与などをしたことにより、損害 (直接・間接を問わず) が発生した場合、弊社は一切その責任を負いかねます。

- 10. 本資料についての詳細に関するお問合せ、その他お気付きの点などがありましたら、弊社営業窓口までご連絡ください。

- 11. 本資料に掲載されている会社名、商品名は、各社の商標または登録商標です。

©Seiko Epson Corporation 2022, All rights reserved.

# ETM63J 改訂履歴

| Rev. No. | Date       | Page      | Description                                                                                                |

|----------|------------|-----------|------------------------------------------------------------------------------------------------------------|

| 01       | 2021/12/06 | All       | 新規登録                                                                                                       |

|          |            | 8<br>98   | VDD = VBAT = GND の状態を 10 秒以上保持を 100ms 以上保持に修正しました。         2.2.1 電源投入シーケンス         5.6 電源投入特性              |

| 02       | 2022/10/12 | 43<br>100 | 43ページ <i>バックアップ電池実装時の注意</i> を新たに追加しました<br>この追記に伴い 100 ページ <i>"7実装上の注意事項"</i> の「バックアップ電池実装」の<br>記述は削除されました。 |

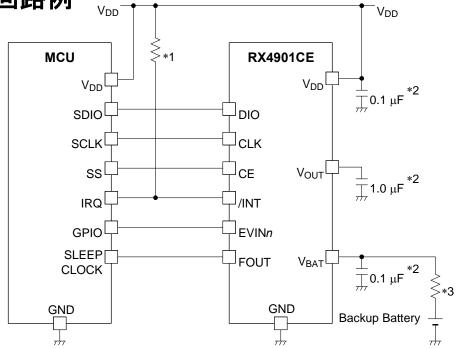

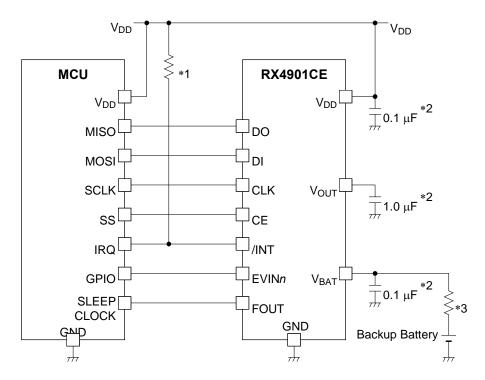

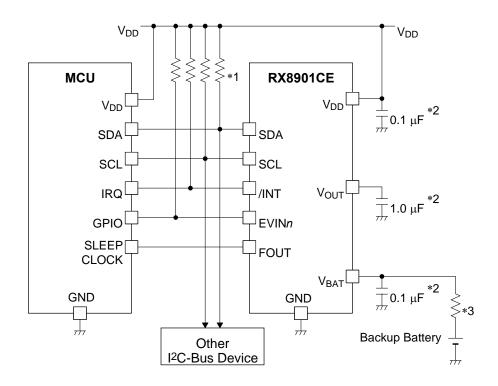

|          |            | 101 102   | 参考回路例注意書き *1 *2 *3 を改訂しました。各回路例の電池をBackup Battery に統一しました。                                                 |

|          |            | 93        | <i>消費電流11</i> の条件説明を改訂しました。                                                                                |

|          |            |           |                                                                                                            |

# はじめに

本書は、セイコーエプソン製RTC(リアルタイムクロック) モジュールRX4901CEおよびRX8901CEの機能、制御方法、仕様、電気的特性を記載したアプリケーションマニュアルです。RX4901CE/RX8901CEを搭載する製品の設計者向けに作成されています。

RX4901CEはSPI、RX8901CEはI<sup>2</sup>C-Busを介してホストデバイスからアクセスします。これらのインターフェイスの動作および制御方法については、ホストデバイスのマニュアル等を参照してください。

# 本書内の表記や記号について

#### 数値の表記

本マニュアルは、10進数、2進数、16進数の数値を扱います。

10進数 例: 1, 10, 123 (一般的な数値や日付、時刻など)

2進数 例: 0b0, 0b10, 0b1111 (制御ビットの設定値、読み出し値など)

16進数 例: 0x0, 0xF, 0xFF (アドレスやレジスターの設定値など)

# レジスター/ビット名の表記

本マニュアルではレジスター名とビット名を次のように記載しています。

レジスター名: レジスターSEC

ビット名: TSTP INTE.STOPビット

レジスターTSTP INTE内のSTOPビットを表します。

TCTL.FSEL[1:0]ビット

レジスターTCTL内のFSEL1とFSEL0ビットの2ビットを表します。

# チャネル番号の表記

タイムスタンプ機能にはチャネルごとに同一機能を持つ端子や制御ビットが用意されています。この端子名やビット名にはチャネル番号 (例:  $1 \sim 3$ ) が含まれています。特に分けて説明する必要がない場合、本書ではこの数値を"n"として複数チャネルを一括して説明しています。また、同一機能のビットでもビット数が異なる場合は、ビット番号を"x"と表記しています。その他、名称の一部が共通な複数のビットを"\*\*\*"を使用し、一つにまとめている場合もあります。

端子名: EVIN<u>1</u>、EVIN<u>2</u>、EVIN<u>3</u> → EVIN*n*

ビット名: EVIN\_EN.EVIN<u>1</u>EN、EVIN\_EN.EVIN<u>2</u>EN、EVIN\_EN.EVIN<u>2</u>EN

$\rightarrow$  EVIN EN.EVINnEN

BUF1 STAT.PTR[5:0], BUF2 STAT.PTR[3:0], BUF3 STAT.PTR[3:0]

$\rightarrow$  BUF*n* STAT.PTR[*x*:0]

EVIN EN.EVIN1CPEN、CAP EN.VBATLCPENなど

→ \*\*\*CPEN

# 目 次

|   | ET         | M63J 改訂履歴                                      | i        |

|---|------------|------------------------------------------------|----------|

|   |            | 43ページバックアップ電池実装時の注意 を新たに追加しました                 |          |

|   | は          | じめに                                            | II       |

|   | <b>A</b> - | 書内の表記や記号について                                   |          |

|   |            | 数値の表記レジスター/ビット名の表記                             |          |

|   |            | チャネル番号の表記                                      | ii       |

|   | 目          | 次 iii                                          | !!       |

|   | • •        |                                                |          |

| 1 | 概團         | ቒ<br>ጚ፟                                        | 1        |

|   | 1.1        | 特長                                             | 1        |

|   |            |                                                |          |

|   | 1.2        | ブロック図                                          |          |

|   |            | RX4901CE                                       |          |

|   |            | RX8901CE                                       |          |

|   |            | 端子                                             |          |

|   | 1.3        |                                                |          |

|   |            | RX4901CE                                       |          |

|   | , ,        | RX8901CE                                       |          |

|   | 1.3        | 5.2 端子説明<br>記号の意味                              |          |

|   |            |                                                |          |

| 2 | 電源         | ほと初期化                                          | 6        |

|   | 2.1        | 電源                                             | A        |

|   |            | —····                                          |          |

|   | 2.2        | 初期化                                            |          |

|   | 2.2        | -5                                             |          |

|   | 2.2        |                                                |          |

|   | 2.2        | 3 初期設定<br>初期設定手順                               |          |

|   |            |                                                |          |

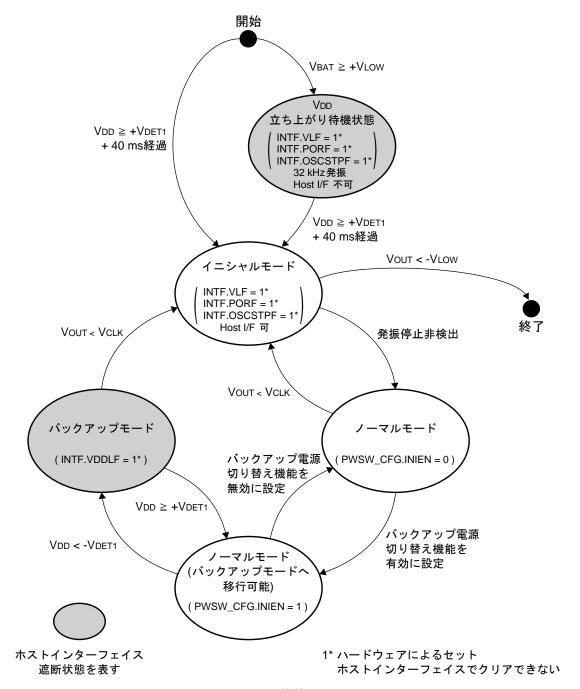

|   | 2.3        | 動作モード                                          | 11       |

|   |            | V <sub>DD</sub> 立ち上がり待機状態                      |          |

|   |            | イニシャルモード<br>ノーマルモード                            |          |

|   |            | ノーマルモード (バックアップモードへ移行可能)                       | 11<br>11 |

|   |            | バックアップモード                                      | 11       |

| _ | ت داخل     |                                                |          |

| 3 | 機能         |                                                |          |

|   | 3.1        | ホストインターフェイス                                    | 13       |

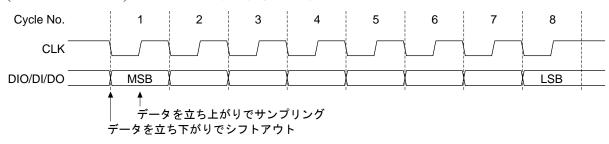

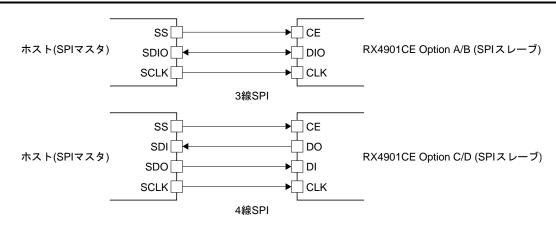

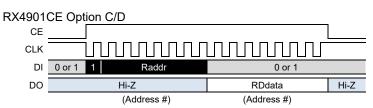

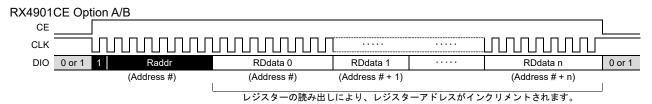

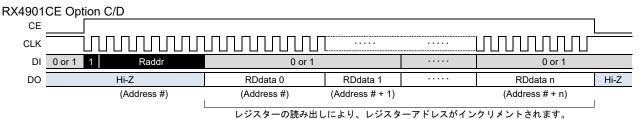

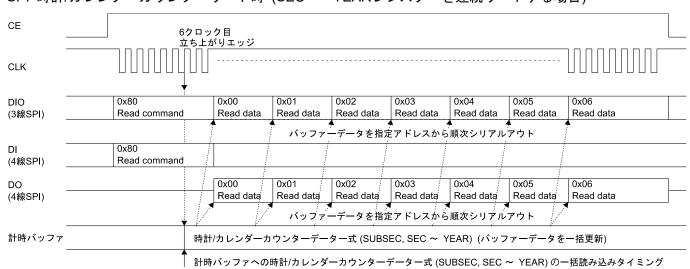

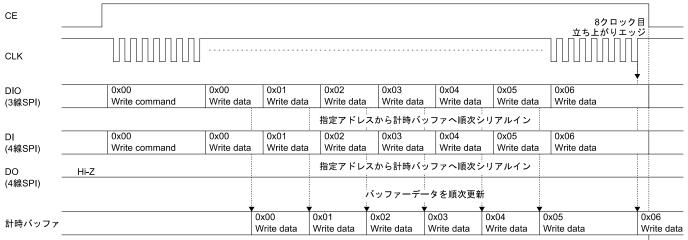

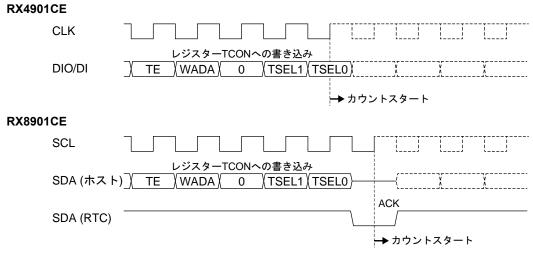

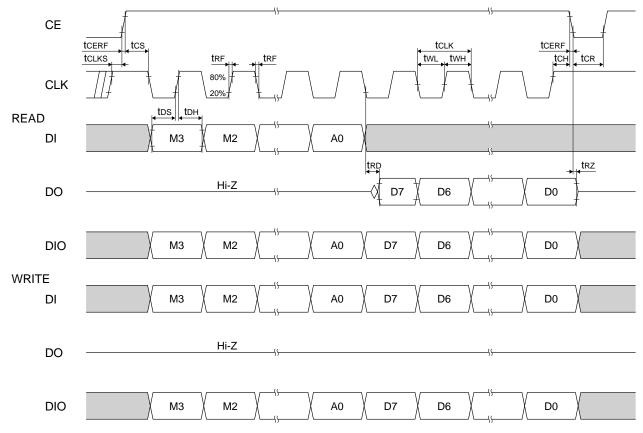

|   | 3.1        | .1 RX4901CE レジスターへのアクセス (SPI)                  | 13       |

|   |            | SPI インターフェイス端子                                 | 13       |

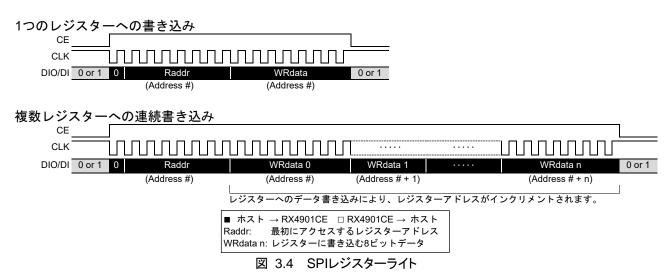

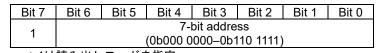

|   |            | レジスターライト                                       |          |

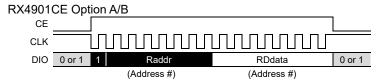

|   | ^ -        | レジスターリード                                       | 15       |

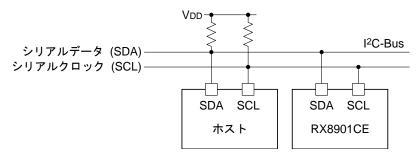

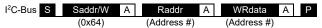

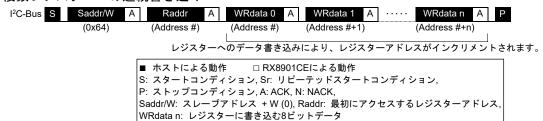

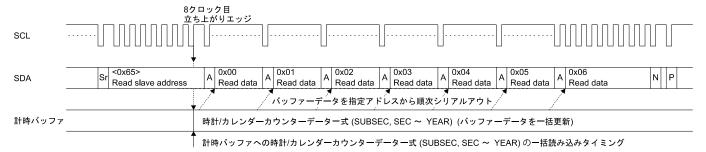

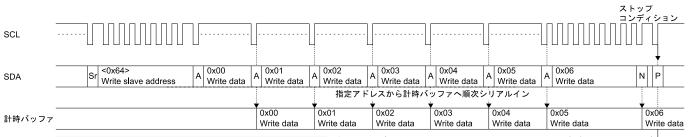

|   | 3.1        | .2 RX8901CE レジスターへのアクセス (I <sup>2</sup> C-Bus) | 16       |

|   |            | PG-Bus インダーフェイス垢于                              |          |

|   |            | レジスターライト                                       |          |

|   |            | レジスターリード                                       |          |

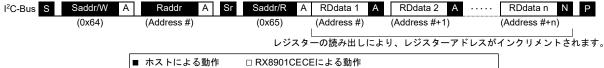

|   | 3 2        | 時計/カレンダー機能                                     |          |

|   | 3.2        |                                                |          |

|   | 3.2        |                                                |          |

|   | 0.2        | 計F                                             | 19       |

|   |            | 時計/カレンダーの初期設定と計時の開始                            |          |

|   |            | 時計/カレンダーの読み出し                                  | 21       |

|   |            | うるう年の判定                                        |          |

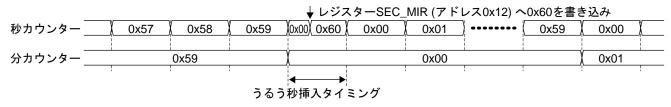

|   |            | うるう秒の挿入手順                                      | 22       |

|   | 3.3        | 温度補償機能                                         | 23       |

|   | 3.3        | 5.1 動作                                         | 23       |

|   |            | 温度補償間隔の設定                                      | 23       |

|   |            | 温度補償動作フラグ VTMPLF フラグ (0x0E)                    | 23       |

|   |            |                                                |          |

| 3.4 時                                                         | 刻更新割り込み機能                                                                                                                                                                                                                                                                                                                                                                            | 24                                                                                                                                     |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.1                                                         | 概要                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                     |

| 3.4.2                                                         | 動作                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

| 3.4.2                                                         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|                                                               | 割り込み周期の選択                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

|                                                               | 割り込み許可/禁止手順                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

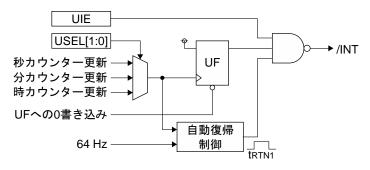

|                                                               | 割り込み動作                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                                                                                     |

|                                                               | — 144 AL                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| 3.5 Y                                                         | ラーム機能                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

| 3.5.1                                                         | 概要                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                     |

| 3.5.2                                                         | 動作                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                     |

| 0.0.2                                                         | プラーム設定手順                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|                                                               | アラーム設定例                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

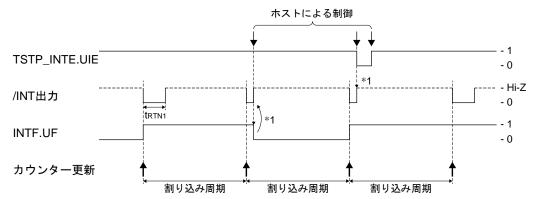

|                                                               | アラーム割り込み                                                                                                                                                                                                                                                                                                                                                                             | 28                                                                                                                                     |

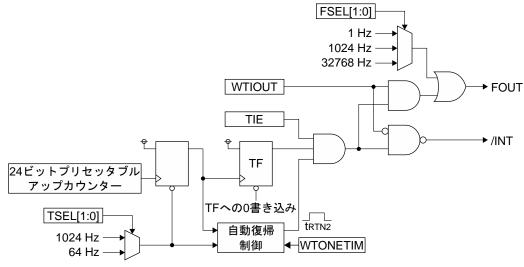

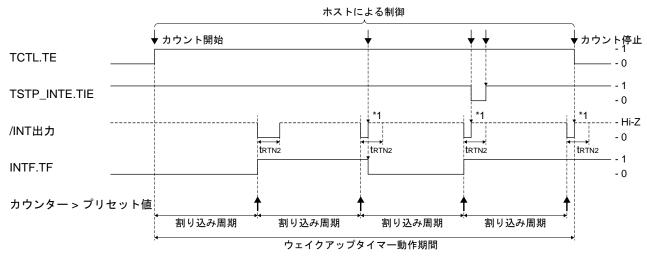

| 3.6 ウ                                                         | ェイクアップタイマー機能                                                                                                                                                                                                                                                                                                                                                                         | 29                                                                                                                                     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

| 3.6.1                                                         | 概要                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

| 3.6.2                                                         | 動作                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

|                                                               | ソースクロック                                                                                                                                                                                                                                                                                                                                                                              | 29                                                                                                                                     |

|                                                               | プリセットデータ (ウェイクアップタイマー割り込み周期)                                                                                                                                                                                                                                                                                                                                                         | 29                                                                                                                                     |

|                                                               | カウント動作条件                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

|                                                               | ウェイクアップタイマー設定手順                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                                                                                     |

|                                                               | リエイグアップダイマー 政化士順                                                                                                                                                                                                                                                                                                                                                                     | 30                                                                                                                                     |

|                                                               | カウントアップの開始                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|                                                               | 一時停止                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                                                                                                     |

|                                                               | カウンターデータの読み出し                                                                                                                                                                                                                                                                                                                                                                        | 32                                                                                                                                     |

|                                                               | カウンターのリセット                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                     |

|                                                               | ウェイクアップタイマー割り込み                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                                     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

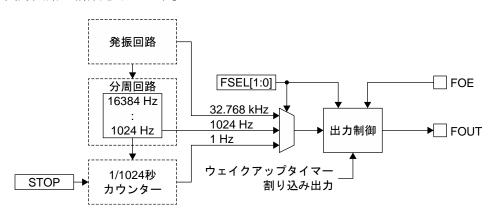

| 3.7 FC                                                        | DUT 出力機能                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                                                                                     |

| 3.7.1                                                         | 概要                                                                                                                                                                                                                                                                                                                                                                                   | 34                                                                                                                                     |

| 3.7.2                                                         | 動作                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

| 3.7.2                                                         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

|                                                               | 初期設定                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

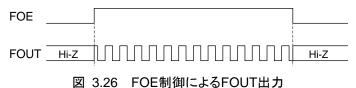

|                                                               | FOUT 出力の制御 (FOE 端子を使用しない場合)                                                                                                                                                                                                                                                                                                                                                          | 34                                                                                                                                     |

|                                                               |                                                                                                                                                                                                                                                                                                                                                                                      | $^{\circ}$                                                                                                                             |

|                                                               | FUUI 出刀の制御 (FUE 斒子を使用する場合)                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                     |

|                                                               | FOUT 出力の制御 (FOE 端子を使用する場合)                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                     |

| +                                                             | FOUT 出力の制御(FOE 端子を使用する場合)<br>FOUT 端子からのウェイクアップタイマー割り込み信号出力                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

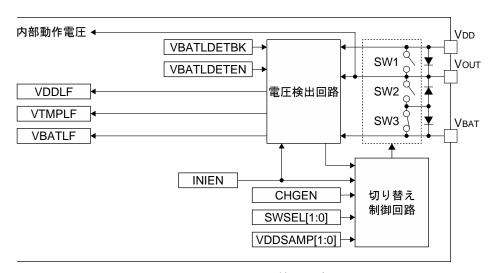

|                                                               | 己監視機能                                                                                                                                                                                                                                                                                                                                                                                | 36                                                                                                                                     |

| <b>3.8 自</b><br>3.8.1                                         |                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                                     |

| 3.8.1                                                         | <b>己監視機能</b><br>概要                                                                                                                                                                                                                                                                                                                                                                   | <b>36</b> 36                                                                                                                           |

|                                                               | <b>己監視機能</b><br>概要<br>自己監視フラグ機能                                                                                                                                                                                                                                                                                                                                                      | <b>36</b> 36 36                                                                                                                        |

| 3.8.1                                                         | <b>己監視機能</b><br>概要<br>自己監視フラグ機能<br>パワーオンリセット発生検出: PORF フラグ                                                                                                                                                                                                                                                                                                                           | <b>36</b> 36 36                                                                                                                        |

| 3.8.1                                                         | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | <b>36</b> 36 36 36                                                                                                                     |

| 3.8.1                                                         | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36                                                                                                       |

| 3.8.1                                                         | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36                                                                                                       |

| 3.8.1                                                         | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36<br>37                                                                                                 |

| 3.8.1                                                         | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36<br>37                                                                                                 |

| 3.8.1<br>3.8.2                                                | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37                                                                                           |

| 3.8.1<br>3.8.2                                                | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37                                                                                           |

| 3.8.1<br>3.8.2                                                | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37                                                                                           |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <mark>己監視機能</mark><br>概要<br>自己監視フラグ機能<br>パワーオンリセット発生検出: PORF フラグ<br>水晶発振停止検出: OSCSTPF フラグ<br>日時データ無効警告: VLF フラグ<br>VoD 電圧低下検出: VDDLF フラグ<br>VBAT 電圧低下検出: VBATLF フラグ<br>温度補償更新停止検出: VTMPLF フラグ<br><b>ックアップ電源切り替え機能</b>                                                                                                                                                                | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>37<br>38                                                                                     |

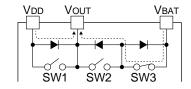

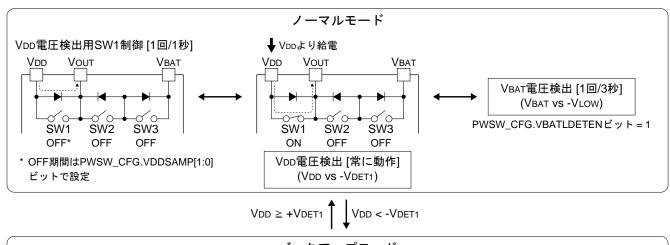

| 3.8.1<br>3.8.2                                                | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38                                                                               |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38                                                                               |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <ul> <li>ご監視機能</li> <li>概要</li> <li>自己監視フラグ機能</li> <li>パワーオンリセット発生検出: PORF フラグ</li> <li>水晶発振停止検出: OSCSTPF フラグ</li> <li>日時データ無効警告: VLF フラグ</li> <li>VoD 電圧低下検出: VDDLF フラグ</li> <li>VBAT 電圧低下検出: VBATLF フラグ</li> <li>温度補償更新停止検出: VTMPLF フラグ</li> <li>ックアップ電源切り替え機能</li> <li>概要</li> <li>動作</li> <li>動作</li> <li>がックアップ電源切り替え機能を使用する場合の設定</li> </ul>                                    | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39                                                                         |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <ul> <li>ご監視機能</li> <li>概要</li> <li>自己監視フラグ機能</li> <li>パワーオンリセット発生検出: PORF フラグ</li> <li>水晶発振停止検出: OSCSTPF フラグ</li> <li>日時データ無効警告: VLF フラグ</li> <li>VoD 電圧低下検出: VDDLF フラグ</li> <li>VBAT 電圧低下検出: VBATLF フラグ</li> <li>温度補償更新停止検出: VTMPLF フラグ</li> <li>ックアップ電源切り替え機能</li> <li>概要</li> <li>動作</li> <li>動作</li> <li>がックアップ電源切り替え機能を使用する場合の設定</li> <li>バックアップ電源切り替え機能を使用しない場合の設定</li> </ul> | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39                                                             |

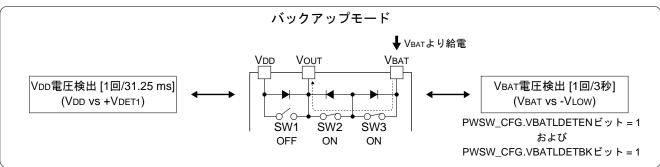

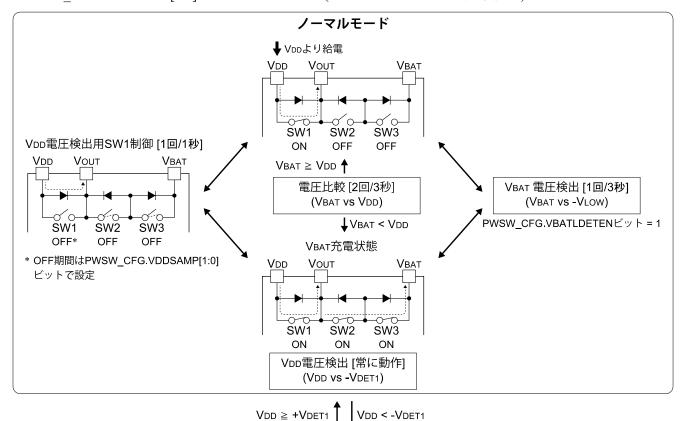

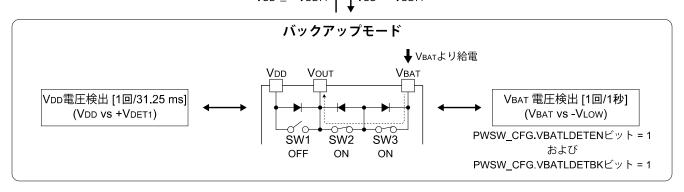

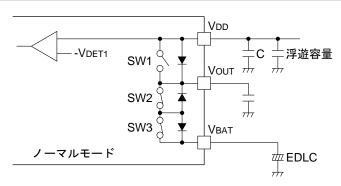

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <b>己監視機能</b> 概要         自己監視フラグ機能       パワーオンリセット発生検出: PORF フラグ         水晶発振停止検出: OSCSTPF フラグ       小品発振停止検出: OSCSTPF フラグ         日時データ無効警告: VLF フラグ       VDD 電圧低下検出: VBATLF フラグ         VBAT 電圧低下検出: VBATLF フラグ       温度補償更新停止検出: VTMPLF フラグ         場内でする場合の設定       ボックアップ電源切り替え機能を使用する場合の設定         バックアップ電源切り替え機能を使用しない場合の設定       バックアップ電源切り替えの動作                             | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>39                                                       |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <ul> <li>ご監視機能</li> <li>概要</li> <li>自己監視フラグ機能</li> <li>パワーオンリセット発生検出: PORF フラグ</li> <li>水晶発振停止検出: OSCSTPF フラグ</li> <li>日時データ無効警告: VLF フラグ</li> <li>VoD 電圧低下検出: VDDLF フラグ</li> <li>VBAT 電圧低下検出: VBATLF フラグ</li> <li>温度補償更新停止検出: VTMPLF フラグ</li> <li>ックアップ電源切り替え機能</li> <li>概要</li> <li>動作</li> <li>動作</li> <li>がックアップ電源切り替え機能を使用する場合の設定</li> <li>バックアップ電源切り替え機能を使用しない場合の設定</li> </ul> | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>39                                                       |

| 3.8.1<br>3.8.2<br><b>3.9</b> / 3.9.1                          | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43                                                             |

| 3.8.1<br>3.8.2<br>3.9 / 3.9.1<br>3.9.2                        | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>38<br>39<br>43<br>43                                                       |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2                     | される                                                                                                                                                                                                                                                                                                                                                                                  | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>43<br>44                                                 |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2                     | される                                                                                                                                                                                                                                                                                                                                                                                  | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>43<br>44                                                 |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2<br>3.10 タ<br>3.10.1 | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>43<br>44                                                 |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2<br>3.10 タ<br>3.10.1 | <b>己監視機能</b>                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>43<br>44<br>44<br>45                                     |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2<br>3.10 タ<br>3.10.1 | 世界である。    記憶視機能                                                                                                                                                                                                                                                                                                                                                                      | 36<br>36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>44<br>45<br>45                                     |

| 3.8.1<br>3.8.2<br>3.9 バ<br>3.9.1<br>3.9.2<br>3.10 タ<br>3.10.1 | 記記視機能                                                                                                                                                                                                                                                                                                                                                                                | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>44<br>45<br>45<br>47                                     |

| 3.8.1<br>3.8.2<br>3.9.7<br>3.9.1<br>3.9.2<br>3.10.1<br>3.10.2 | 記記視機能                                                                                                                                                                                                                                                                                                                                                                                | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>45<br>47<br>47                                     |

| 3.8.1<br>3.8.2<br>3.9.7<br>3.9.1<br>3.9.2<br>3.10.1<br>3.10.2 | 記記視機能                                                                                                                                                                                                                                                                                                                                                                                | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>45<br>47<br>47                                     |

| 3.8.1<br>3.8.2<br>3.9.7<br>3.9.1<br>3.9.2<br>3.10.1<br>3.10.2 | 世界機能                                                                                                                                                                                                                                                                                                                                                                                 | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>47<br>47<br>47                                     |

| 3.8.1<br>3.8.2<br>3.9.7<br>3.9.1<br>3.9.2<br>3.10.1<br>3.10.2 | 世界機能                                                                                                                                                                                                                                                                                                                                                                                 | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>47<br>47<br>47                                     |

| 3.8.1<br>3.8.2<br>3.9.7<br>3.9.1<br>3.9.2<br>3.10.1<br>3.10.2 | では、                                                                                                                                                                                                                                                                                                                                                                                  | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>47<br>47<br>47<br>47<br>47                   |

| 3.8.1<br>3.8.2<br>3.9 /\( \) 3.9.1<br>3.9.2 3.10.3 3.10.3     | 世界                                                                                                                                                                                                                                                                                                                                                                                   | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>47<br>47<br>47<br>47<br>47<br>48<br>49       |

| 3.8.1<br>3.8.2<br>3.9 /\( \) 3.9.1<br>3.9.2 3.10.3 3.10.3     | では、                                                                                                                                                                                                                                                                                                                                                                                  | 36<br>36<br>36<br>36<br>36<br>37<br>37<br>38<br>38<br>38<br>39<br>39<br>43<br>44<br>45<br>47<br>47<br>47<br>47<br>47<br>48<br>49<br>49 |

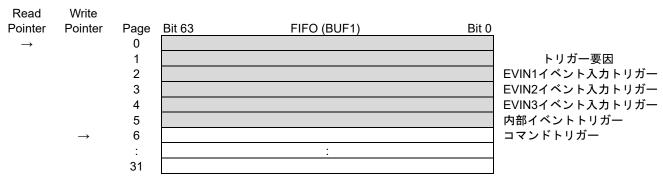

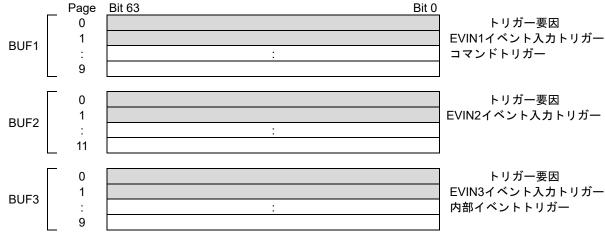

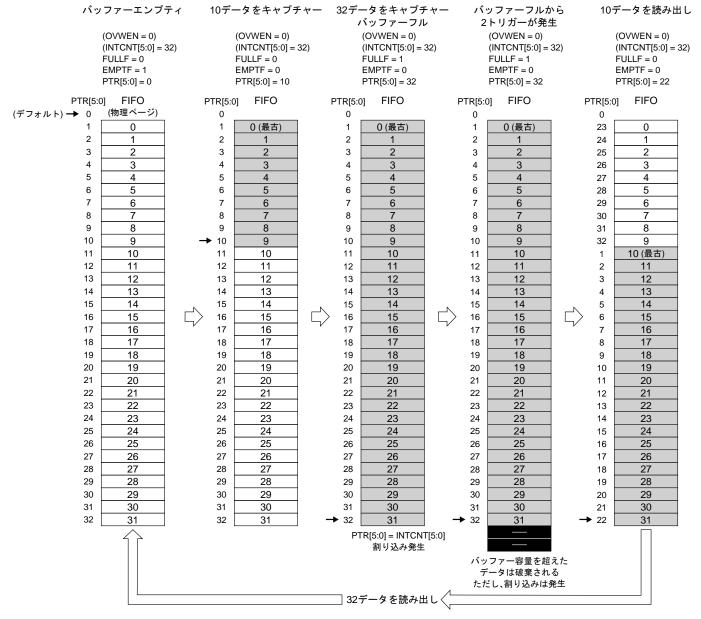

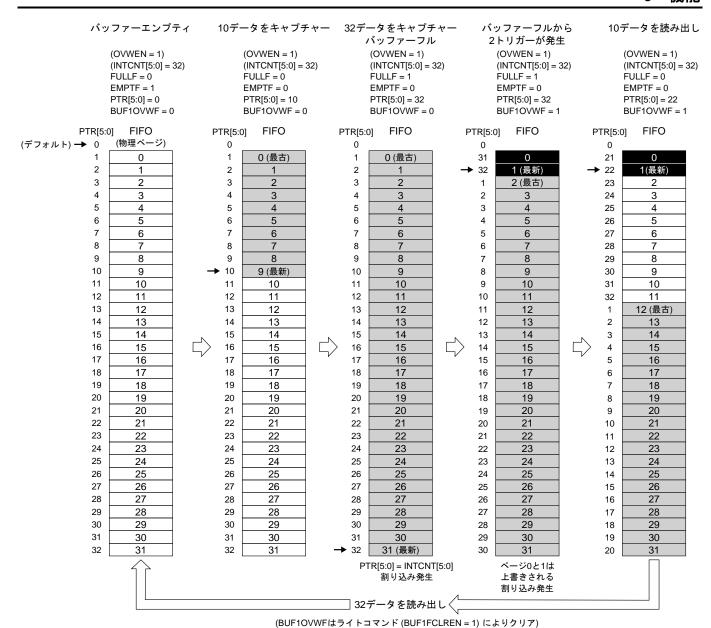

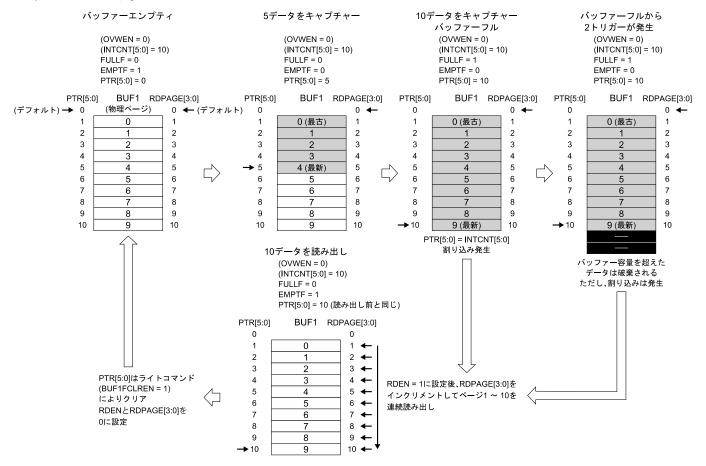

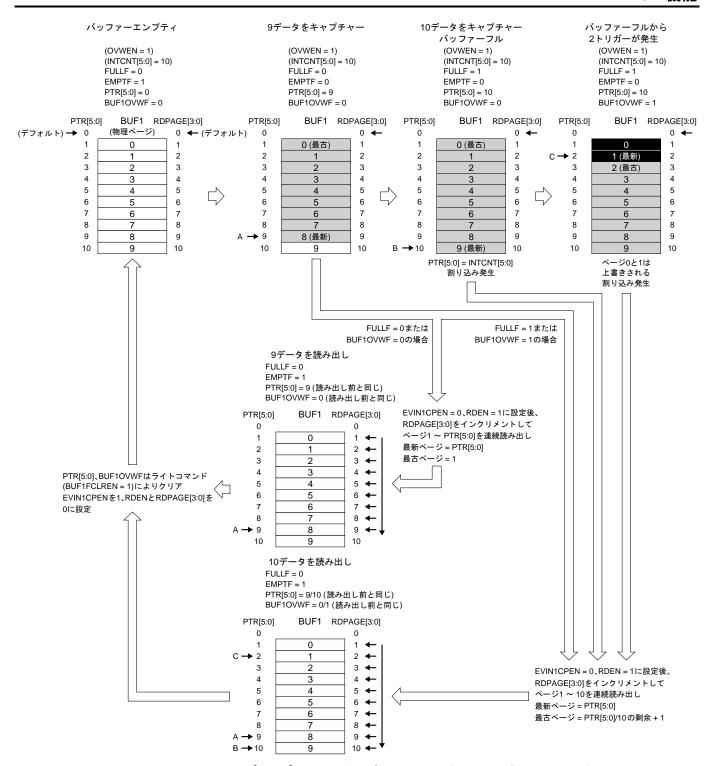

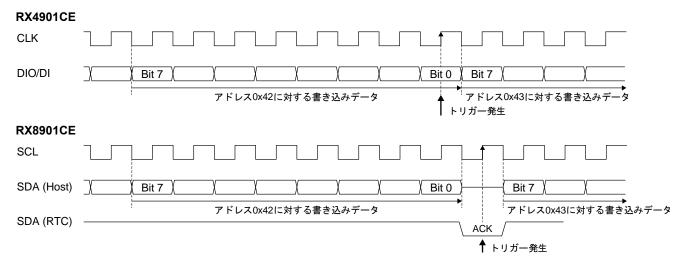

|      | タイムスタンプキャプチャー動作                                                        | 52 |

|------|------------------------------------------------------------------------|----|

|      | コマンドトリガーの発行                                                            |    |

|      | タイムスタンプデータの読み出し                                                        |    |

|      | タイムスタンプナータの読み出し                                                        |    |

|      | タイムスタンプデータのクリア                                                         | 61 |

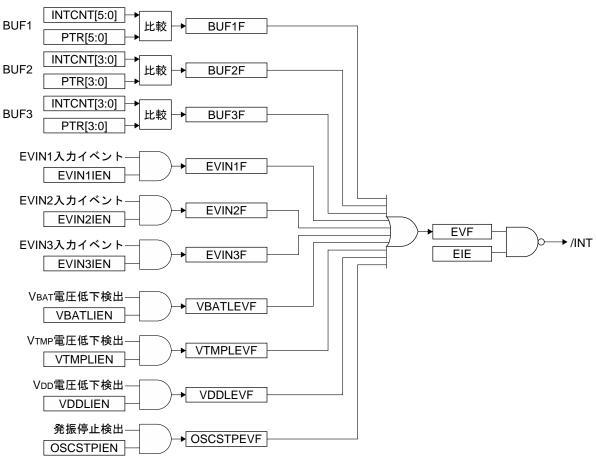

| 3.1  | 10.5 タイムスタンプ (イベント検出) 割り込み                                             | 62 |

|      |                                                                        |    |

| 4 レシ | <sup>;</sup> フスター                                                      | 63 |

| 4.4  | レジスター一覧                                                                | 63 |

| 4. 1 |                                                                        |    |

|      | 記号の意味                                                                  |    |

|      | Bank 0                                                                 |    |

|      | Bank 1                                                                 | 64 |

|      | Bank 2                                                                 | 64 |

|      | Bank 3                                                                 | 65 |

|      | Bank 4                                                                 |    |

|      | Bank 5                                                                 |    |

|      | Bank 6 (FIFO モードでのタイムスタンプデータ読み出し時)                                     |    |

|      | Bank o (FIFO モートでのダイム人ダノフナーダ読み直し時)                                     | 00 |

|      | Bank 6 (ダイレクトモードでのタイムスタンプデータ読み出し時)                                     | 66 |

|      | Bank 6 (SRAM モード)                                                      | 66 |

| 4.2  | レジスター詳細説明                                                              | 67 |

| 4.2  |                                                                        |    |

|      | 0x00: SEC (Second Data)                                                |    |

|      | 0x01: MIN (Minute Data)                                                |    |

|      | 0x02: HOUR (Hour Data)                                                 | 67 |

|      | 0x03: WEEKDAY (Day-of-Week Data)                                       | 67 |

|      | 0x04: DAY (Day Data)                                                   |    |

|      | 0x05: MONTH (Month Data)                                               |    |

|      | 0x06: YEAR (Year Data)                                                 |    |

|      | 0x07: ALM_MIN (Minute Alarm)                                           |    |

|      | 0x08: ALM HOUR (Hour Alarm)                                            |    |

|      |                                                                        |    |

|      | 0x09: ALM_WEEKDAY (Day-of-Week Alarm / Day Alarm)                      |    |

|      | 0x0A: WTCNT_L (Wakeup Timer Counter Low)                               |    |

|      | 0x0B: WTCNT_M (Wakeup Timer Counter Middle)                            | 71 |

|      | 0x0C: WTCNT_H (Wakeup Timer Counter High)                              | 71 |

|      | 0x0D: TCTL (Timer Control)                                             | 71 |

|      | 0x0E: INTF (Status Flag)                                               | 73 |

|      | 0x0F: TSTP`INTE (Timer Stop and Interrupt Enable)                      |    |

|      | 0x10: SUBSEC L (Sub-Second Data Low)                                   |    |

|      | 0x11: SUBSEC H (Sub-Second Data High)                                  |    |

|      | 0x12: SEC_MIR (Mirrored Second Data, = 0x00)                           |    |

|      |                                                                        |    |

|      | 0x13: MIN_MIR (Mirrored Minute Data, = 0x01)                           |    |

|      | 0x14: HOUR_MIR (Mirrored Hour Data, = 0x02)                            |    |

|      | 0x15: WEEKDAY_MIR (Mirrored Day-of-Week Data, = 0x03)                  |    |

|      | 0x16: DAY_MIR (Mirrored Day Data, = 0x04)                              | 76 |

|      | 0x17: MONTH_MIR (Mirrored Month Data, = 0x05)                          | 76 |

|      | 0x18: YEAR_MIR (Mirrored Year Data, = 0x06)                            |    |

|      | 0x20: EVIN EN (Event Input Enable)                                     |    |

|      | 0x21: EVIN1 CFG (EVIN1 Configuration)                                  |    |

|      | 0x23: EVIN2_CFG (EVIN2 Configuration)                                  |    |

|      | 0x25: EVIN3_CFG (EVIN3 Configuration)                                  |    |

|      |                                                                        |    |

|      | 0x22: EVIN1_FLT (EVIN1 Noise Filter)                                   |    |

|      | 0x24: EVIN2_FLT (EVIN2 Noise Filter)                                   |    |

|      | 0x26: EVIN3_FLT (EVIN3 Noise Filter)                                   |    |

|      | 0x27: BUF1_CFG1 (BUF1 Configuration 1)                                 |    |

|      | 0x2A: BUF2_CFG1 (BUF2 Configuration 1)                                 |    |

|      | 0x2D: BUF3 CFG1 (BUF3 Configuration 1)                                 | 79 |

|      | 0x28: BUF1_STAT (BUF1 Status)                                          |    |

|      | 0x2B: BUF2_STAT (BUF2 Status)                                          |    |

|      | 0x2E: BUF3_STAT (BUF3 Status)                                          |    |

|      | 0x29: BUF1_CFG2 (BUF1 Configuration 2)                                 | ΩΩ |

|      |                                                                        |    |

|      | 0x2C: BUF2_CFG2 (BUF2 Configuration 2)                                 |    |

|      | 0x2F: BUF3_CFG2 (BUF3 Configuration 2)                                 |    |

|      | 0x30: ALM_SEC (Second Alarm)                                           | 81 |

|      | 0x31: ALM_MIN_MIR (Mirrored Minute Alarm, = 0x07)                      | 82 |

|      | 0x32: ALM HOUR MIR (Mirrored Hour Alarm, = 0x08)                       | 82 |

|      | 0x33: ALM_WEEKDAY_MIR (Mirrored Day-of-Week Alarm / Day Alarm, = 0x09) | 82 |

|      | 0x34: UPDISEL (Time Update Interrupt Select)                           | 82 |

|      | - ' - '                                                                |    |

|   |            | 0x37: PWSW_CFG (Power Switch Configuration)                               |          |

|---|------------|---------------------------------------------------------------------------|----------|

|   |            | 0x38: WTICFG (Wakeup Timer Interrupt Configuration)                       |          |

|   |            | 0x39: WTCTL (Wakeup Timer Control)                                        |          |

|   |            | 0x3A: WTCNT_L_MIR (Mirrored Wakeup Timer Counter Low, = 0x0A)             |          |

|   |            | 0x3B: WTCNT_M_MIR (Mirrored Wakeup Timer Counter Middle, = 0x0B)          |          |

|   |            | 0x3C: WTCNT_H_MIR (Mirrored Wakeup Timer Counter High, = 0x0C)            |          |

|   |            | 0x41: WRCMD_CFG (Write Command Configuration)                             |          |

|   |            | 0x42: WRCMD_TRG (Write Command Trigger)                                   |          |

|   |            | 0x43: EVNT_INTE (Event Interrupt Enable)                                  |          |

|   |            | 0x44: CAP_EN (Capture Enable)<br>0x46: BUF_INTF (Buffer Interrupt Factor) | 00<br>00 |

|   |            | 0x47: EVNT_INTF (Event Interrupt Factor)                                  |          |

|   |            | 0x4F: BUF_FULLF (Buffer Full Flag)                                        |          |

|   |            | 0x4F: BUF_OVWF (Buffer Overwrite Flag)                                    |          |

|   |            | 0x51: EVIN1 EVCNT (EVIN1 Event Counter)                                   |          |

|   |            | 0x52: EVIN2_EVCNT (EVIN2 Event Counter)                                   |          |

|   |            | 0x53: EVIN3 EVCNT (EVIN3 Event Counter)                                   |          |

|   |            | 0x54: EVINMON (EVIN Monitor)                                              |          |

|   |            | ,                                                                         |          |

| 5 | 電          | 的特性                                                                       | 92       |

|   | 5.1        | 絶対最大定格                                                                    | 92       |

|   | _          | #2.27 以入之11<br>推奨動作条件                                                     |          |

|   | 5.2        |                                                                           |          |

|   | 5.3        | 周波数特性                                                                     | 92       |

|   | 5.4        | DC 特性                                                                     | 93       |

|   |            | DC 特性                                                                     |          |

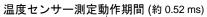

|   |            | 温度補償回路動作と消費電流                                                             |          |

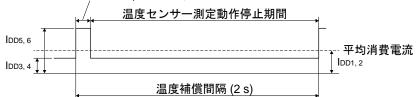

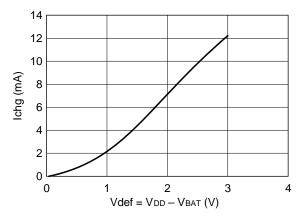

|   |            | バックアップ電源切り替え素子特性 (参考)                                                     | 94       |

|   | <b>5 5</b> | AC 特性                                                                     | 96       |

|   | 5.5        | RX4901CE AC 特性                                                            |          |

|   |            | RX8901CE AC 特性                                                            |          |

|   | - ^        |                                                                           |          |

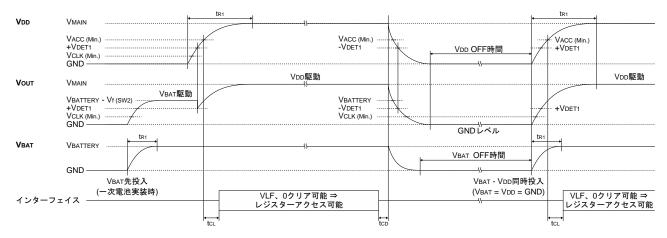

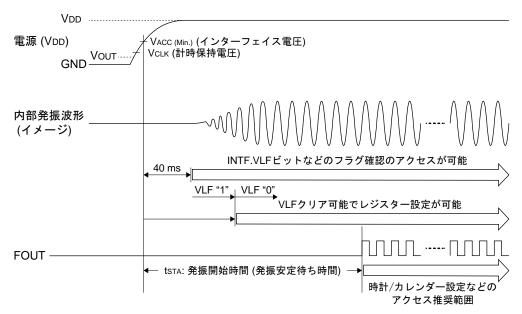

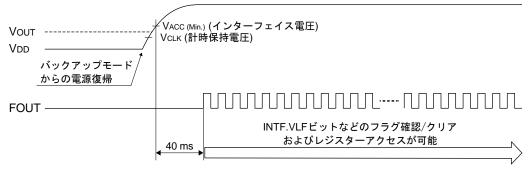

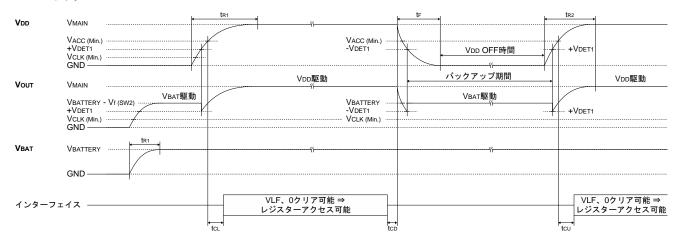

|   |            | 電源投入特性                                                                    |          |

| 6 | 18         | ケージ                                                                       | 99       |

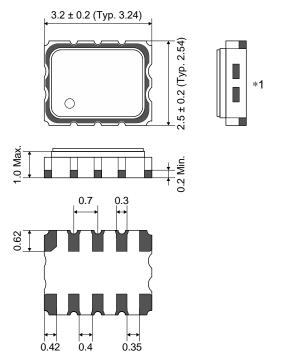

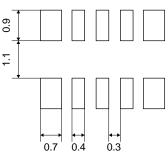

|   | 6.1        | 外形寸法図                                                                     | 99       |

|   |            | イル する日                                                                    |          |

|   |            |                                                                           |          |

| 7 | 実          | 上の注意事項                                                                    | 100      |

|   |            | 静電気                                                                       |          |

|   |            |                                                                           |          |

|   |            | 入力端子の電圧                                                                   |          |

|   |            | 未使用入力端子の処理                                                                |          |

|   |            | はんだ付け温度                                                                   |          |

|   |            | 実装機                                                                       |          |

|   |            | 超音波洗浄                                                                     |          |

|   |            | 実装方向                                                                      |          |

|   |            | 端子間リーク                                                                    | 100      |

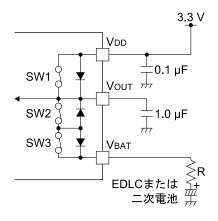

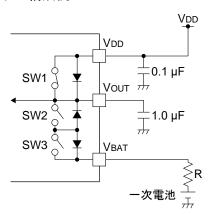

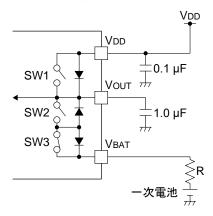

| 8 | 参:         | 回路例                                                                       | 101      |

|   | _          |                                                                           |          |

| 义 | ]表-        |                                                                           |          |

|   |            | 図                                                                         | 103      |

# 1 概要

RX4901CE/RX8901CEは、32.768 kHzデジタル温度補償型水晶発振器 (DTCXO) を搭載したRTC (リアルタイムクロック) モジュールです。RTCの基本機能である時刻カレンダー、時刻アラーム、ウェイクアップタイマー、時刻更新割り込みに加え、外部または内部のイベント発生日時を最大32回記録可能なタイムスタンプなどの、豊富な機能があります。さらに、主電源への電流逆流防止制御を含むバックアップ電源自動切り替え機能や、常時温度補正された32.768 kHzのクロック出力と、独自の低消費電流技術の組み合わせにより、各種システムの時計カレンダー情報やタイムスタンプの長期運用を実現します。

RX4901CE XS A0 (3)

- ① 機種名 CE タイプパッケージ 3.2 x 2.5 x 1.0 mm

- ② 周波数精度

- 3 Pin Option A0~D0 : Option A~D

表 1.1 製品ラインナップ

| 製品名称                 | インターフェイス             | デフォル     | 田油粉草中*3   |                   |

|----------------------|----------------------|----------|-----------|-------------------|

| <b>製</b> 面 <b>4</b>  | 1 ンダーフェイス            | Pin 4 *1 | Pin 10 *2 | <b>■ 周波数精度</b> *3 |

| RX4901CE Option A XS | 3線SPI                | FOUT     | EVIN2     | XS                |

| RX4901CE Option A XB |                      |          |           | XB                |

| RX4901CE Option B XS |                      | EVIN3    |           | XS                |

| RX4901CE Option B XB |                      |          |           | XB                |

| RX4901CE Option C XS | 4線SPI                | FOUT     | DI        | XS                |

| RX4901CE Option C XB |                      |          |           | XB                |

| RX4901CE Option D XS |                      | EVIN3    |           | XS                |

| RX4901CE Option D XB |                      |          |           | XB                |

| RX8901CE Option A XS | I <sup>2</sup> C-Bus | FOUT     | EVIN2     | XS                |

| RX8901CE Option A XB |                      |          |           | XB                |

| RX8901CE Option B XS |                      | EVIN3    |           | XS                |

| RX8901CE Option B XB |                      |          |           | XB                |

<sup>\*1</sup> 製品によりPin 4のデフォルト機能が異なります。起動後にレジスターの設定によってFOUT (クロック出力) 端子またはEVIN3 (外部イベント入力) 端子に切り替え可能です。

# 1.1 特長

表 1.2 特長

|                  | X 12 NX       |                                                                                                                                          |           |             |          |                      |          |  |  |

|------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|----------|----------------------|----------|--|--|

| 製品ラインナップ<br>     |               |                                                                                                                                          | RX4       | RX8901CE    |          |                      |          |  |  |

|                  |               | Option A                                                                                                                                 | Option B  | Option C    | Option D | Option A             | Option B |  |  |

| ホストイ             | ンターフェイス       | 3線SPI                                                                                                                                    |           | 4線SPI       |          | I <sup>2</sup> C-Bus |          |  |  |

| 水晶発振             | 器             | 32.768 kHzデジタ                                                                                                                            | ル温度補償型水   | 晶発振器 (DTCXO | )を搭載     |                      |          |  |  |

| 時計/カレ            | ンダー           | ・秒、分、時、日、月、年をカウントするBCDカウンターならびに曜日カウンター、 1/1024秒をカウントするバイナリーカウンターを搭載 ・うるう年の自動補正機能搭載 うるう秒補正操作可能 ・時刻更新割り込みを発生可能 (1秒、1分、1時間の各時刻 (カウンター) 更新時) |           |             |          |                      |          |  |  |

| ウェイク             | アップタイマー       | •976.56 µs ~ 32年周期で割り込みを発生可能<br>•主電源動作あるいはバックアップ電源動作の積算時間計として使用可能                                                                        |           |             |          |                      |          |  |  |

| アラーム             |               | 秒から日 (または曜日) までを指定し、割り込みを発生可能                                                                                                            |           |             |          |                      |          |  |  |

|                  | トリガー要因        | 外部イベント (EVIN) 入力、RTC内電圧低下/発振停止検出、ホストからのコマンド入力                                                                                            |           |             |          |                      |          |  |  |

| スタンプ             | 記録データ         | 1/1024秒 ~ 1秒、秒、分、時、日、月、年、トリガー要因、内部ステータス                                                                                                  |           |             |          |                      |          |  |  |

|                  | 記録可能なイベント数    | 最大32イベント                                                                                                                                 |           |             |          |                      |          |  |  |

|                  | 外部イベント入力端子 *1 | (EVIN2)、(EVIN3)                                                                                                                          | )         | (EVIN3)     |          | EVIN1、(EVIN2)、       | (EVIN3)  |  |  |

| SRAMメモリー         |               | 容量、256バイトを搭載 (タイムスタンプデータの記録領域と兼用)                                                                                                        |           |             |          |                      |          |  |  |

| クロック出力 (FOUT) *1 |               | <ul><li>32.768 kHz、1024 Hz、または1 Hz出力を選択可能</li><li>レジスターまたはFOE入力 (レジスター選択) により出力を制御可能</li></ul>                                           |           |             |          |                      |          |  |  |

| 自己監視             | <b>後能</b>     | 発振停止、V <sub>DD</sub> /V <sub>B</sub>                                                                                                     | AT電圧低下を検b | 出し割り込みを発生   | 可能       |                      |          |  |  |

<sup>\*2</sup> Option A/B Pin 10のデフォルト機能はEVIN2です。起動後にレジスターの設定によってFOE (FOUT出力制御) 端子に切り替え可能です。

<sup>\*3</sup> XSとXB (精度) の違いについては、"5.3 周波数特性"の周波数安定度を参照してください。

| 製品ラインナップ                | RX4901CE RX8901CE                                                                                                                      |          |          |          |          | 01CE     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|

|                         | Option A                                                                                                                               | Option B | Option C | Option D | Option A | Option B |

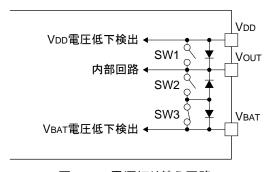

| バックアップ電源切り替え機能          | • V <sub>DD</sub> /V <sub>BAT</sub> 電圧を監視し、ノーマルモード (V <sub>DD</sub> 動作) とバックアップモード (V <sub>BAT</sub> 動作) を切り替え<br>• バックアップ二次電池/容量の充電制御 |          |          |          |          |          |

| 動作電圧 (V <sub>DD</sub> ) | 1.60 V ~ 5.5 V                                                                                                                         |          |          |          |          |          |

| 動作温度                    | -40 °C ~ +105 °C                                                                                                                       |          |          |          |          |          |

<sup>\*1</sup> EVIN3入力とFOUT出力はどちらか一方のみ使用可能です。EVIN2入力とFOE入力はどちらか一方のみ使用可能です。

# 1.2 ブロック図

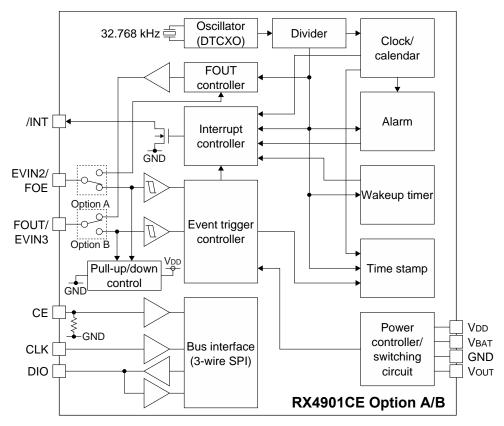

#### **RX4901CE**

図 1.1 RX4901CE Option A/Bブロック図

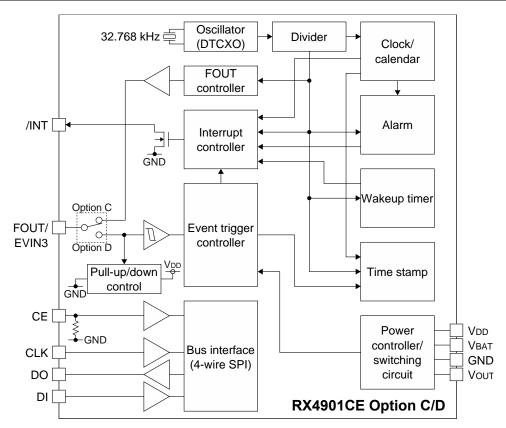

図 1.2 RX4901CE Option C/Dブロック図

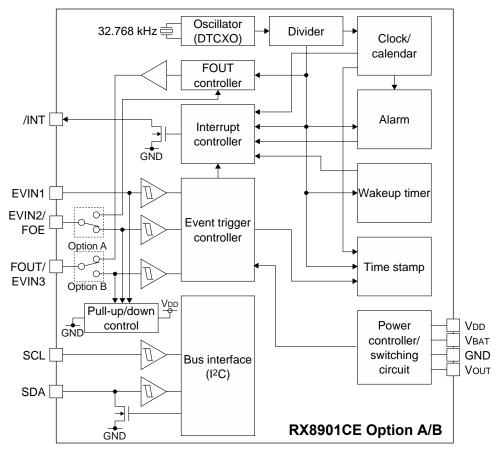

#### **RX8901CE**

図 1.3 RX8901CE Option A/Bブロック図

# 1.3 端子

# 1.3.1 端子配置図

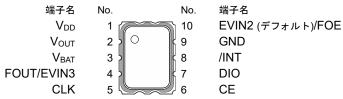

#### **RX4901CE**

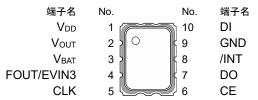

図 1.4 RX4901CE Option A/B端子配置図

図 1.5 RX4901CE Option C/D端子配置図

#### **RX8901CE**

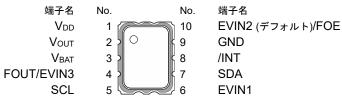

図 1.6 RX8901CE Option A/B端子配置図

# 1.3.2 端子説明

## 記号の意味

入出力 I: 入力端子

O:

出力端子

I/O:

入出力端子

初期状態 Hi-Z: ハイインピーダンス

PU: プルアップ PD: プルダウン

機種別欄 ✓: あり

\*1: EVIN3入力とFOUT出力はどちらか一方のみ使用可能 (レジスターで選択) \*2: EVIN2入力とFOE入力はどちらか一方のみ使用可能 (レジスターで選択)

-: なし

表 1.3 端子説明

| 端子名              | 1 ш+ | 初期状態           | 機能                                                                                                                                                    |                | RX49           | 01CE          |                | RX8901CE       |                |  |

|------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---------------|----------------|----------------|----------------|--|

| <b>斒</b> 十名      | 人田刀  | 彻别认思           | 懐眊                                                                                                                                                    | Α              | В              | С             | D              | Α              | В              |  |

| EVIN1            | I    | PU<br>(1 MΩ)   | 外部イベント入力端子<br>これらの端子の入力信号がタイムスタンプのトリガーとして使用されま                                                                                                        | _              | -              | _             | -              | 1              | 1              |  |

| EVIN2            |      |                | す (バックアップ時でも検出可能)。                                                                                                                                    | <b>✓</b> *2    | <b>✓</b> *2    | _             | _              | <b>✓</b> *2    | <b>✓</b> *2    |  |

| EVIN3            | -    |                | プログラマブルなプルアップ/プルダウン抵抗とノイズフィルターを内蔵しています。                                                                                                               | <b>(✓)</b> *1  | <b>✓</b> *1    | <b>(</b> ✓)*1 | <b>✓</b> *1    | <b>(</b> ✓)*1  | ✓*1            |  |

| CLK              | I    | Hi-Z           | 3線/4線SPIシリアルクロック入力端子<br>本端子はノーマルモードではフローティング状態禁止です。バックアップモードではフローティング状態が許可されます。                                                                       | 1              | 1              | 1             | 1              | _              | _              |  |

| DIO              | I/O  | Hi-Z           | 3線SPIシリアルデータ入出力端子<br>本端子はノーマルモードではフローティング状態禁止です。バックアップモードではフローティング状態が許可されます。                                                                          | 1              | 1              | _             | _              | _              | _              |  |

| DO               | 0    | Hi-Z           | 4線SPIシリアルデータ出力端子                                                                                                                                      | _              | _              | 1             | 1              | _              | -              |  |

| DI               | I    | Hi-Z           | 4線SPIシリアルデータ入力端子<br>本端子はノーマルモードではフローティング状態禁止です。バックアップモードではフローティング状態が許可されます。                                                                           | _              | _              | 1             | 1              | _              | _              |  |

| CE               | I    | PD<br>(300 kΩ) | 3線/4線SPIスレーブセレクト入力端子<br>プルダウン抵抗を内蔵しています。                                                                                                              | 1              | 1              | 1             | 1              | -              | _              |  |

| SCL              | I    | Hi-Z           | I <sup>2</sup> C-Busシリアルクロック入力端子<br>本端子はノーマルモードではフローティング状態禁止です。バックアップモードではフローティング状態が許可されます。<br>外部で5.5 Vまでプルアップすることが可能です。                              | _              | _              | _             | _              | 1              | 1              |  |

| SDA              | I/O  | Hi-Z           | I <sup>2</sup> C-Busシリアルデータ入出力端子 (N-chオープンドレイン)<br>本端子はノーマルモードではフローティング状態禁止です。バックアップモードではフローティング状態が許可されます。<br>外部で5.5 Vまでプルアップすることが可能です。               | _              | _              | _             | _              | •              | 1              |  |

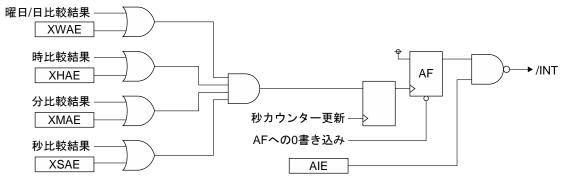

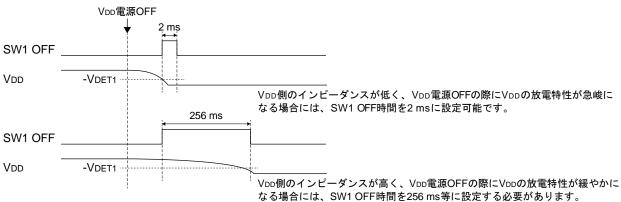

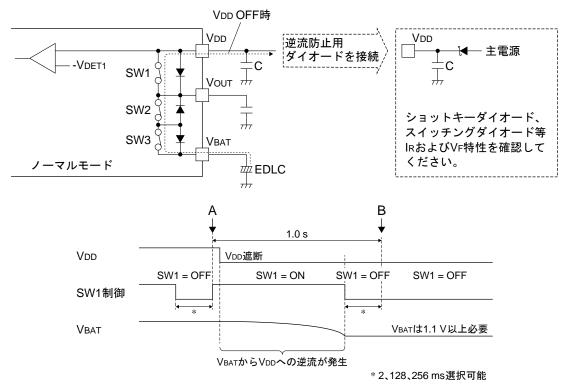

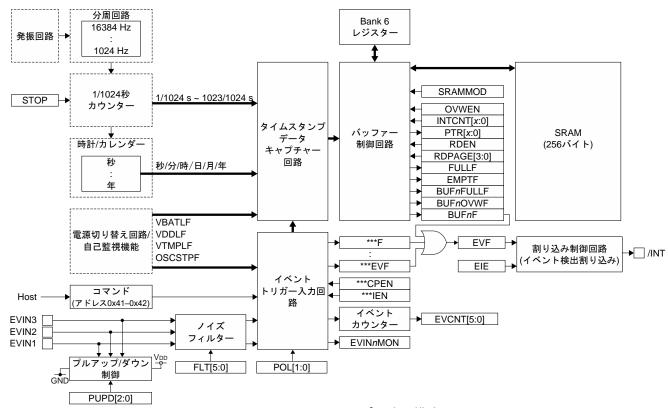

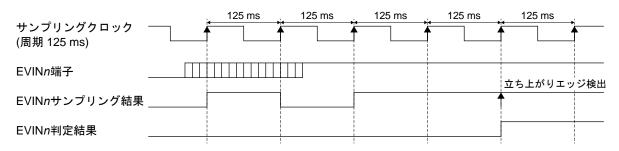

| FOUT             | 0    | Hi-Z           | クロック出力端子 (CMOS)<br>32.768 kHz (デフォルト)、1024 Hz、1 Hz出力が選択可能です。<br>ウェイクアップタイマー割り込み出力 (CMOS) に切り替え可能です。                                                   | <b>✓</b> *1    | ( <b>✓</b> )*1 | <b>✓</b> *1   | ( <b>✓</b> )*1 | <b>✓</b> *1    | ( <b>✓</b> )*1 |  |